[{"keyword":"\ubc84\ud29c\ubc84","rank":0},{"keyword":"\ube14\ub8e8\uc544\uce74","rank":0},{"keyword":"\uc720\ud76c\uc655","rank":9},{"keyword":"\ud2b8\ub9ad\uceec","rank":-1},{"keyword":"\ub9bc\ubc84\uc2a4","rank":4},{"keyword":"\uc6d0\uc2e0","rank":0},{"keyword":"\uc6d0\ud53c\uc2a4","rank":-2},{"keyword":"\ub9d0\ub538","rank":-4},{"keyword":"@","rank":-1},{"keyword":"\ud751\ubc31","rank":0},{"keyword":"\uc18c\uc8042","rank":"new"},{"keyword":"\ud751\ubc31\uc694\ub9ac\uc0ac","rank":5},{"keyword":"\uc778\ubc29","rank":5},{"keyword":"\uc18c\uc804","rank":"new"},{"keyword":"\ud65c\ud611\uc804","rank":1},{"keyword":"\uc6cc\ud574\uba38","rank":-3},{"keyword":"\uac74\ub2f4","rank":5},{"keyword":"\ub2c8\ucf00","rank":1},{"keyword":"\ud638\uc5f0","rank":"new"},{"keyword":"\ub9c8\uce74\uc624\ud1a1","rank":"new"},{"keyword":"\ub77c\uc624","rank":"new"},{"keyword":"\ub864","rank":-8}]

(IP보기클릭)49.161.***.***

(IP보기클릭)211.37.***.***

(IP보기클릭)121.169.***.***

(IP보기클릭)121.169.***.***

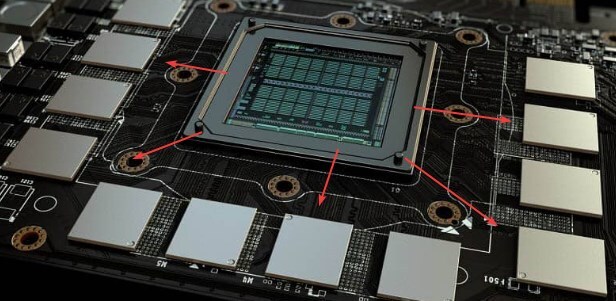

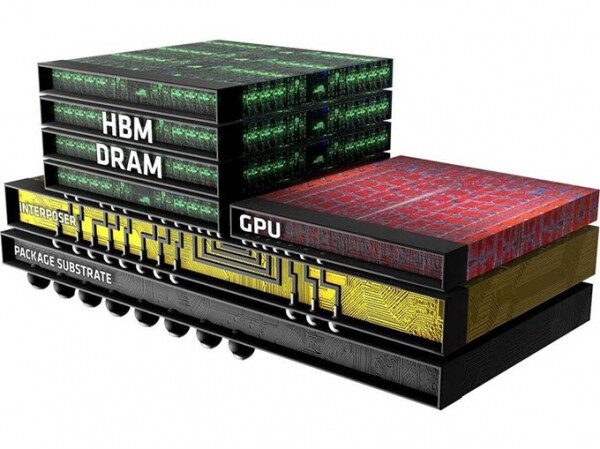

일반적인 DDR, LPDDR, GDDR의 경우 채널당 칩 하나가 할당되고 여기에 데이터핀 개수가 16개~32개 수준에 다른 핀 다 합쳐도 40여개 수준인데 HBM은 HBM3 기준 채널당 64개 +@에 칩 하나에 16개 채널이 묶여있음. 그래서 데이터핀만 1024개, 커맨드 어드레스 핀까지 더하면 거기서 +@ (기억 상 채널당 리페어용이나 다른 목적을 위한 핀까지 다 합치면 아마 100개 쯤 될거) 근데 이렇게 많은 신호를 기존 패키지/PCB에서 신호 선로를 연결하는 건 불가능에 가까움. 그래서 여기서 같이 나온 기술이 실리콘 인터포저, 2.5D 인터포저로 반도체칩 생산 공정의 BEOL(금속 배선) 공정을 갖다가 씀. 일반적인 메모리 - soc간 연결이 (soc 다이) - (soc 패키지) - (pcb) - (디램 패키지) - (디램 다이) 이 순이었다면, HBM의 경우 (soc 다이) - (인터포저) - (디램 다이) 이렇게 감. 이게 하나의 패키지가 되어있고 | 24.05.24 23:10 | | |

(IP보기클릭)172.226.***.***

(IP보기클릭)121.169.***.***

높이도 제덱 스펙으로 정해져있음 그리 높지 않음 | 24.05.24 23:10 | | |