6.1 <<전환 가능한 1.2μm 픽셀 피치 50Mp 픽셀 롤링 셔터 모드와 2.4μm 픽셀 피치 12.5Mp 픽셀 글로벌 셔터 모드를 갖춘 모바일 애플리케이션용 3단 적층 하이브리드 셔터(듀얼 셔터 모드) CMOS 이미지 센서>>

삼성전자, 대한민국

최근 모바일 애플리케이션용 CMOS 이미지 센서(CIS) 개발은 50메가픽셀(Mp) 이상의 초고해상도를 달성하기 위해 픽셀 스케일링에 중점을 두고 있습니다 [1]. 또한 이벤트 비전 센서(EVS)가 적용된 롤링 셔터(RS) CIS를 통해 이미지 품질을 개선하는 등 첨단 적층 공정 기술을 활용한 이미지 센서의 기능 강화가 활발히 진행되고 있습니다 [2].

동시에 글로벌 셔터(GS) CIS는 기존 롤링 셔터(RS) CIS의 한계를 극복할 수 있는 탁월한 대안으로 부상하고 있습니다.

모바일 애플리케이션용 GS CIS는 다음과 같은 장점을 제공합니다:

1) 빠르게 움직이는 물체를 왜곡 없이 포착할 수 있습니다.

2) 모든 픽셀이 동시에 노출되어 플리커 현상에 영향을 받지 않습니다. 반면 RS CIS는 장단 노출 시간 간의 트레이드오프가 필요합니다.

3) 순간 플래시로 인한 플래시 밴딩을 방지할 수 있습니다.

GS CIS는 이러한 장점 덕분에 모바일 기기 사용자에게 향상된 경험을 제공할 잠재력이 있습니다. 그러나 RS CIS에 비해 전압 도메인 GS CIS는 샘플링 커패시터로 인한 높은 랜덤 노이즈(RN) 수준을 나타내며, 이는 적용 가능성을 제한하는 요인이 됩니다.

이에 따라 저희는 RS와 GS 모드를 모두 지원하는 하이브리드 셔터(HS) CIS를 개발하여 각 모드의 장점을 최대한 활용하고자 했습니다. 본 논문에서는 픽셀 내 전압 샘플러를 통해 RS 모드와 GS 모드를 전환할 수 있는 HS CIS를 제안하고 시연하였습니다.

감광 픽셀층은 0.6μm 피치의 200M(16384×12288) 개별 포토다이오드로 구성됩니다. 4개의 개별 포토다이오드가 모여 1.2μm 피치의 50M (8192×6144) 픽셀을 구성하며, RS 모드에서 30fps로 동작합니다. 또한, 16개의 개별 포토다이오드가 모여 2.4μm 피치의 12.5M (4096×3072) 픽셀을 구성하며, RS 및 GS 모드에서 95fps로 동작할 수 있습니다.

추가적으로, HDR 성능을 향상시키기 위해 듀얼 슬로프 게인(DSG) 판독 회로를 적용했습니다.

하이브리드 셔터(HS) CIS는 3층 스택형 웨이퍼 구조로 구성되며, 상층/중간층은 픽셀용, 하층은 로직 회로용입니다. 기존 RS CIS의 성능 및 기능을 유지하기 위해 상층에는 약간 수정된 전통적인 4T 트랜지스터 픽셀 구조를 사용했습니다. 따라서 GS 모드에서도 RS 모드와 동일한 풀웰 캐패시티(FWC) 특성을 가지며, 낮은 변환 이득(LCG)에서는 52ke-입니다.

GS CIS의 랜덤 노이즈(RN) 성능을 개선하기 위해 중간층에는 대용량 DRAM 커패시터 기술을 적용했습니다. 이에 따라 GS 모드에서 높은 변환 이득(HCG) 상태에서 2.4 e- 수준의 낮은 읽기 노이즈(RN)를 달성했습니다.

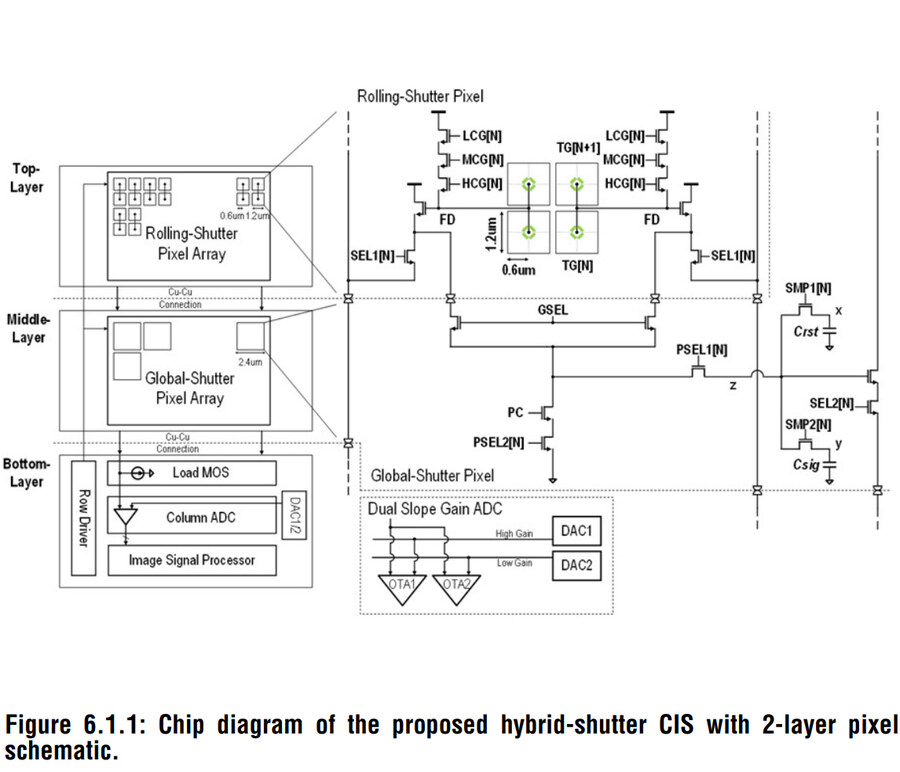

제안된 2층 픽셀 HS CIS 칩 구조는 그림 6.1.1에 나와 있습니다.

상층에는 0.6μm 네 개의 포토다이오드를 활용한 1.2μm 픽셀의 전통적인 공유 픽셀 구조를 적용했습니다. 중간층에는 65nm CIS 공정을 적용하여 전압 영역 GS 동작을 위한 커패시터와 트랜지스터를 배치했으며, 픽셀피치는 2.4μm입니다. 하층에는 28nm 공정을 사용한 아날로그 및 디지털 회로가 포함되어 있습니다.

GS 동작을 위한 픽셀 구조는 이전 논문[3]에 제시된 것과 기본적으로 동일합니다. GSEL 스위치를 추가하여 동작 모드를 선택하고, SEL1 스위치를 추가하여 RS와 동일한 동작을 구현했습니다. GS 모드에서는 FD(Floating Diffusion)에서 수직으로 전하를 합산한 뒤, 중간층에서 수평 전압을 평균하여 각 픽셀의 출력을 전체 픽셀에 걸쳐 동시에 커패시터에 샘플링합니다. 이 과정을 "글로벌 덤프(global dump)"라고 하며, 글로벌 덤프 이후에는 전하를 한 줄씩 롤링 방식으로 읽어들입니다.

전환 가능한 HS CIS의 동작 타이밍 다이어그램은 그림 6.1.2에 나와 있습니다. 세 가지 변환 이득(CG) 조건은 HCG, MCG, LCG 트랜지스터 중 하나를 전환하여 달성합니다. RS 모드의 동작은 기존의 4T 동작과 동일하며, 이때 중간층의 모든 트랜지스터는 비활성화됩니다.

글로벌 덤프(global dump) 동안, 모든 GSEL 및 PSEL2 게이트가 열리며, PC 트랜지스터가 픽셀 내 바이어스 트랜지스터 역할을 합니다.

SMP1과 SMP2 스위치를 통해 FD 노드의 RST와 SIG 신호를 픽셀 내 소스 팔로워(In-pixel SF)를 통해 Crst와 Csig에 각각 샘플링합니다. SMP1과 SMP2가 꺼진 상태에서는 해당 제어선이 간섭원이 될 수 있으며, 다른 트랜지스터의 게이트 및 부유 노드가 커패시터 결합 간섭(capacitive coupling)에 영향을 받을 수 있습니다. 이는 SMP1과 SMP2가 픽셀 출력에 변동을 주어 노이즈를 유발할 수 있으며, 특히 RST와 SIG 샘플링 불일치로 인해 FPN(Fixed Pattern Noise)이 발생할 수 있습니다.

따라서 SMP1과 SMP2 사이의 기생 커패시턴스 차이를 최소화하여 노이즈를 억제하도록 설계했습니다.

롤링 셔터(RS) 읽기 과정에서는, z-노드를 FD 노드 전압으로 미리 충전(precharge)하여 각 ADC 이전의 z-노드 전압이 동일하게 유지되도록 합니다. In-pixel SF를 사용하여 FD를 미리 충전하므로, 별도의 프리차지 스위치가 필요하지 않습니다. 각 z-노드가 미리 충전된 후, 저장 노드와 z-노드 간의 전하 공유가 이루어지고, 이때 SMP1 또는 SMP2가 활성화된 상태에서 각 ADC가 동작합니다.

또한, HDR GS 모드를 위해 DSG(Dual Slope Gain) 모드를 추가했습니다. DSG 모드는 하나의 픽셀 출력에 대해 고/저 아날로그 이득(AG)을 동시에 적용하고, 두 개의 ADC 결과를 합성하여 최종 이미지를 복원합니다[4].

단일 슬로프 ADC에서는 슬로프 조정에 따라 비교기 대역폭이 달라집니다[5]. 특히 높은 AG 설정 시(슬로프가 작을 때) 비교기 대역폭이 좁아집니다.

예를 들어, 한 장면에서 밝은 영역은 AG ×1, 어두운 영역은 AG ×4를 사용하면 어두운 영역의 총 RN이 절반으로 감소하고, 이에 따라 HDR 성능이 6dB 향상됩니다.

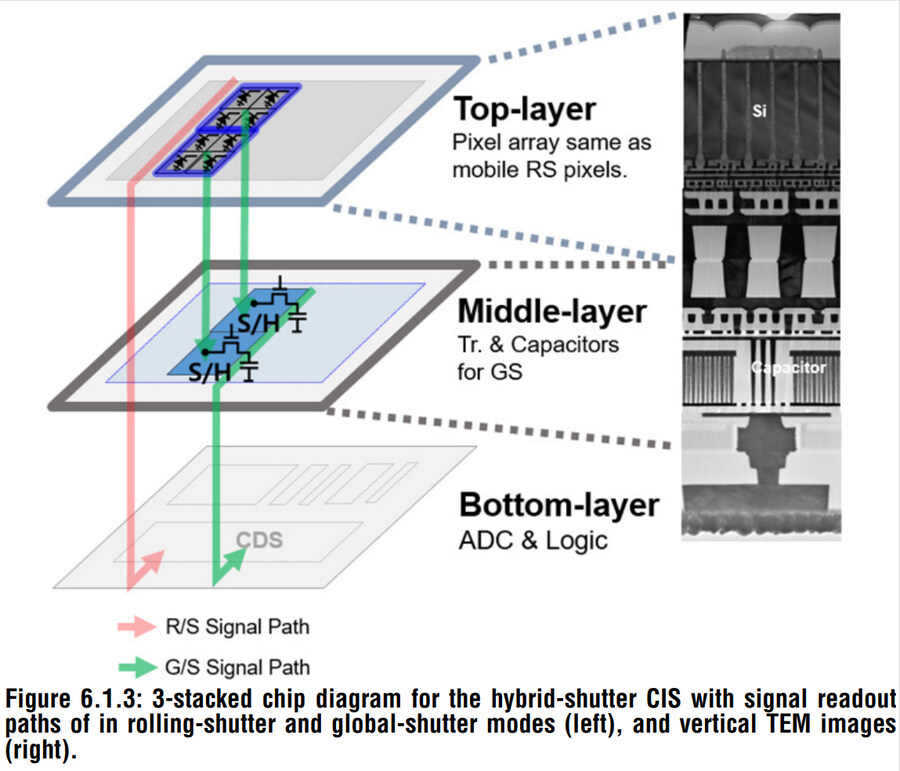

그림 6.1.3은 RS/GS 모드 신호 읽기 경로를 갖는 HS CIS의 3층 칩 구조와 수직 TEM 이미지를 보여줍니다. 상층과 중간층을 연결하기 위해 페이스 투 페이스(face-to-face) 구리 하이브리드 본딩 방식을 사용했습니다.

3층 구조를 형성하기 위해 중간층의 실리콘 기판을 통해 중간층 금속과 하층 금속을 연결하는 페이스 투 페이스 구리 하이브리드 본딩 방법을 적용했습니다[6].

3층 적층 기술을 적용함으로써, 기존 모바일 롤링 셔터 픽셀[7]을 HS CIS의 상층 픽셀로 재사용할 수 있습니다. RS 모드는 상층과 하층만 사용해도 성능 저하 없이 작동합니다.

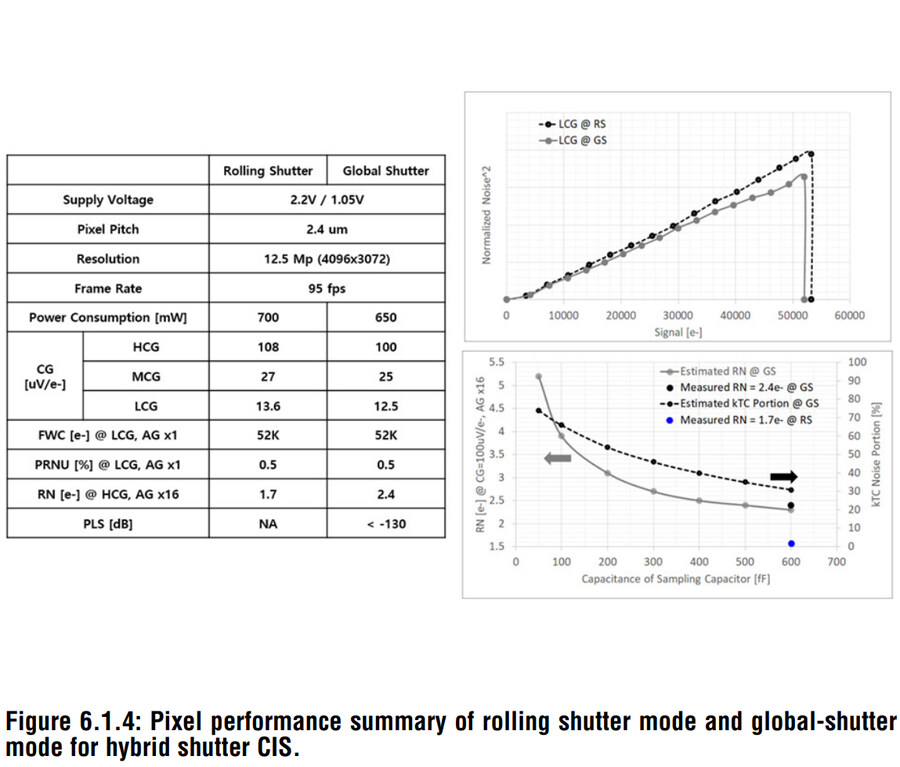

그림 6.1.4는 HS CIS의 RS 및 GS 모드 픽셀 성능 요약이며, 12.5Mp, 95fps에서 실온 조건으로 측정한 결과입니다. 픽셀 및 아날로그 회로의 전원 전압은 2.2V, 디지털 회로는 1.05V입니다. RS 모드와 GS 모드의 소비 전력은 각각 700mW와 650mW입니다.

롤링 셔터(RS) 읽기 과정에서는 수평 전압 평균화를 위해 두 개의 픽셀 부하가 필요하지만, GS 모드에서는 글로벌 덤프(global dump) 동안 이미 수평 전압 평균이 완료되므로 하나의 픽셀 부하만 필요합니다.

따라서 12.5Mp GS 모드의 소비 전력이 12.5Mp RS 모드보다 낮습니다.

GS 모드에서는, 0.6μm 픽셀의 우수한 FWC(풀웰 캐패시티) 특성을 활용해 전하를 합산함으로써, LCG와 AG ×1 설정에서 52 ke- FWC를 얻을 수 있습니다.

RN(랜덤 노이즈) 증가를 최소화하기 위해 대용량 DRAM 커패시터 기술[8]을 적용하여 kTC 노이즈를 억제했습니다. 중간층에 픽셀 내 600fF 샘플링 커패시터를 통합함으로써, HCG와 AG ×16 설정에서 2.4e- RN을 달성했습니다.

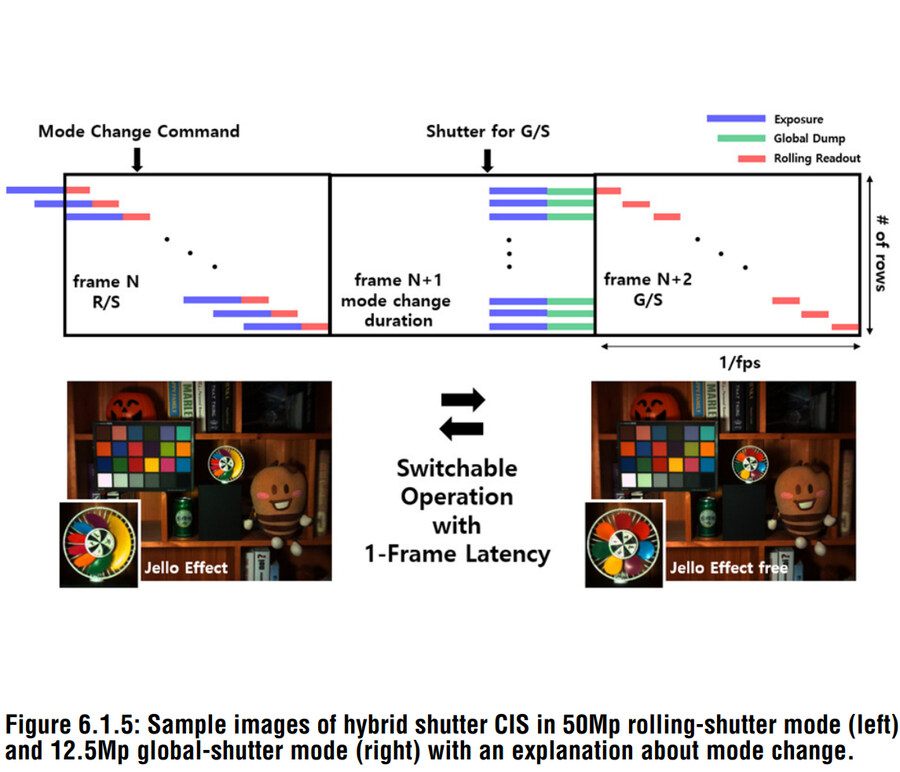

그림 6.1.5는 HS CIS가 50Mp RS 모드(왼쪽)와 12.5Mp GS 모드(오른쪽)에서 촬영한 이미지 샘플을 보여주며, 모드 전환 설명도 포함되어 있습니다. 이 샘플 이미지는 HCG와 AG ×8 동작 조건에서 촬영되었습니다.

GS 모드에서는 젤로 이펙트(jello effect)가 나타나지 않았습니다. 또한, 시스템 레벨에서의 모드 전환 방법도 소개했습니다. 애플리케이션 프로세서 등에서 모드 전환 명령을 수신하면 RS 모드와 GS 모드 간 전환을 1프레임 지연으로 수행할 수 있습니다.

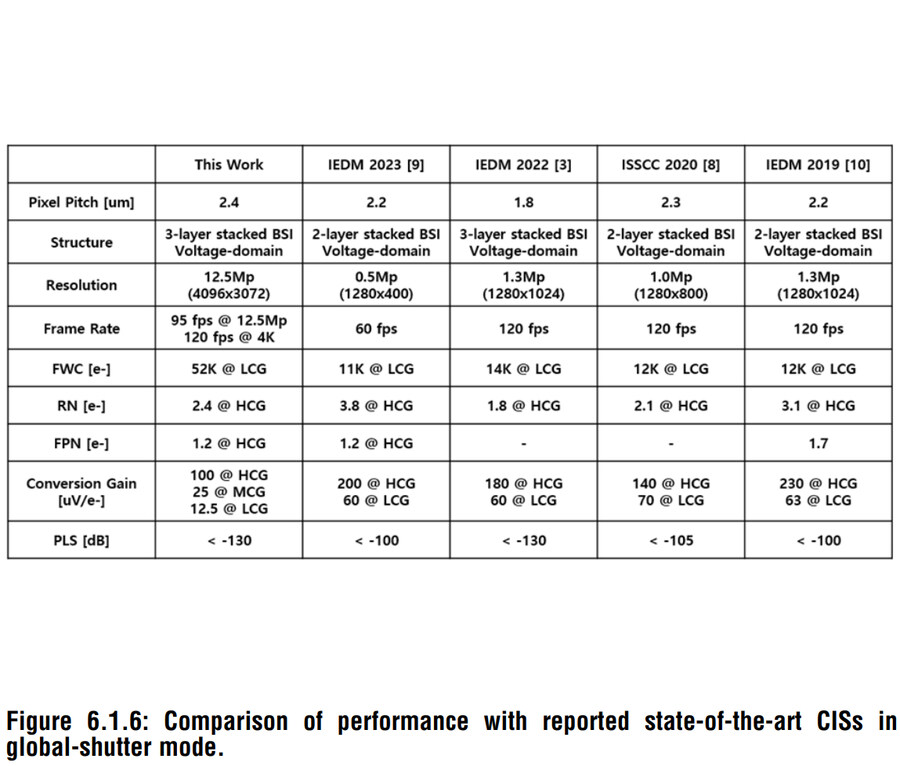

그림 6.1.6은 GS 모드에서의 HS CIS 성능을 기존 최신 CIS와 비교한 결과입니다. 비교한 참고 장치들 중에서 52 ke- FWC는 가장 높은 수준입니다. 1.2e- FPN은 SMP1 및 SMP2 스위치와 관련된 기생 커패시턴스를 줄여 실온에서 달성했습니다.

하지만, 변환 이득(CG) 감소로 인해 2.4e- RN은 이전 연구 결과[3]보다 더 크게 나타났습니다. 그러나 전압 단위 기준으로는 이 CIS의 RN 성능이 개선되었습니다.

그림 6.1.7은 3층 적층 HS CIS의 현미경 사진입니다. 우리는 HS CIS의 이미지 왜곡 없는 GS 모드가 동적 녹화 환경/조건에서 모바일 애플리케이션에 대한 더 나은 사용자 경험을 제공하고 창출할 수 있다고 기대합니다.

(IP보기클릭)2.56.***.***

(IP보기클릭)182.220.***.***