현업 6년차 학사 나부랭이 ㅈ문가의 지식이니 틀린 부분이 있을수 있읍니다

구글에 HCI(hot carrier injection), NBTI(negative bias temperature instability), Electromigration 등에 대한 내용을 검색해보면 자세한 설명이 나옵니다

아니면 transistor aging 으로 검색해보셔도 좋습니다

우선 알아둬야할 것은, 대부분의 반도체 칩은 한번쯤 들어봤을 MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor)를 사용한다

다른 트랜지스터도 그렇지만 보통 소스, 드레인, 게이트, 바디로 구성되는 MOSFET은 기본적으로 메탈 게이트에 걸리는 전압이 일정 기준을 넘었냐 넘지 않았냐에 따라 on/off가 되는 스위칭 소자라고 보면 된다

한번쯤 들어봤을 핀펫FinFET은 MOS의 모양을 지느러미(Fin) 형태로 한 것이고,

차세대 공정으로 이야기가 나오는 GAA(Gate-all-around)FET의 경우 MOS로 아예 채널을 감싸버린 케이스라고 보면 된다

PMIC 같은 곳에서는 BJT(Bipolar Juction Transistor)를 사용하는 경우도 많은데 일단 이건 일단 둘째치고,

반도체 칩에 있는 반도체 회로는 이 수많은 트랜지스터와 이 트랜지스터를 연결하는 금속 선로를 가지고 있다.

당장 기본적인 셀 중 하나인 입력이 2개인 NAND2만 해도 트랜지스터 4개 묶음이다.

고작 셀 하나가 이 정도이니 현 세대 반도체 칩 하나에 트랜지스터 수십억개가 들어가니 어쩌니 하는 것.

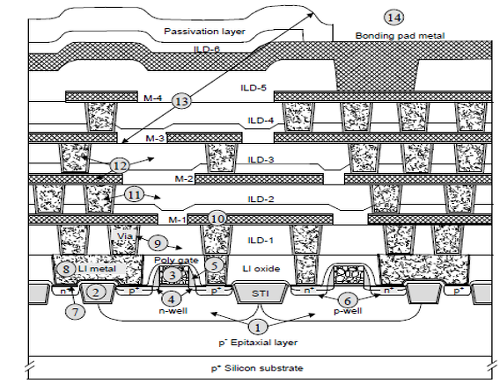

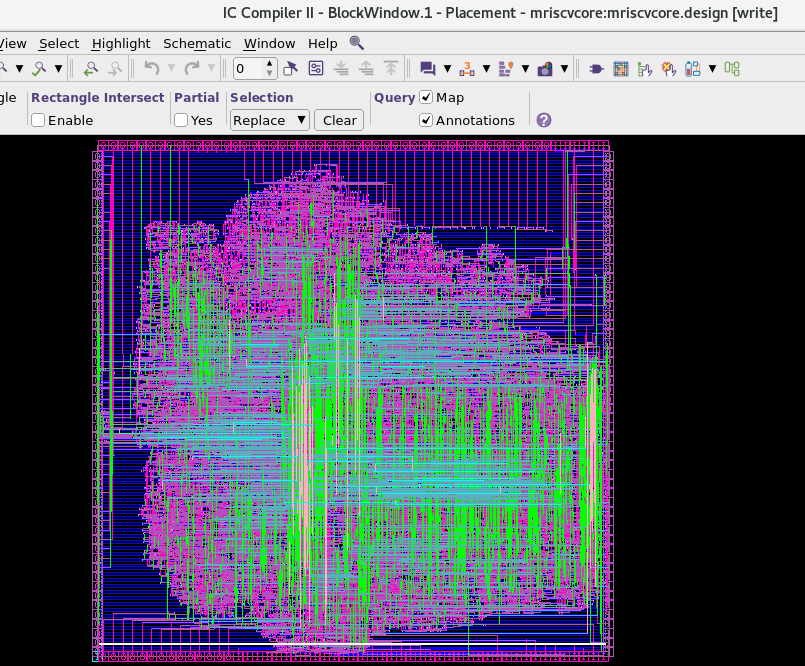

여하튼 잡설은 치우고 대부분의 반도체 칩의 단면도와 설계도(일반적으로 반도체 레이아웃, GDS로 불리는 그거)는 아래 그림과 같다.

(1) 반도체 칩의 단면도

(2) 반도체 칩 설계 프로그램 화면(ICC라는 대표적인 place & route 프로그램)

(화면 깨진거 아닙니다)

반도체칩 수명 이야기하는데 이 두개를 왜 이야기하냐면

반도체 칩 수명에 관해서 1. 트랜지스터 자체의 특성 열화와 2. 금속 선로의 열화 두가지 이야기를 하려고 하기 때문이다

1. 트랜지스터 특성 열화

트랜지스터는 기본적으로 on/off를 제어하는 스위치인데 (물론 아날로그 회로에서는 다른 특성을 활용하기도 한다)

게이트에 걸리는 전압이 일정 이상 되면 채널이 형성되고, 전자/정공(이 둘을 합쳐 캐리어Carrier라고 한다)이 채널을 통과하여 전류가 흐르게 되는데, 이렇게 채널이 형성되냐 안되냐가 트랜지스터의 on/off라고 보면 된다.

이 on/off의 기준점이 되는 값을 문턱 전압(Threshold Voltage, 일반적으로 Vth로 표기한다)이라고 하며,

트랜지스터의 속도는 (공급 전압 - 문턱 전압)에 영향을 받는다.

아주 정확한 설명은 아니겠지만, 대충 설명하면

트랜지스터의 속도가 빠르다

= 신호가 전달 된 후 트랜지스터로 구성된 연산 회로의 출력이 바뀌는 시간이 짧다

= 더 짧은 시간 안에 더 많은 연산을 하고 그 값을 주고 받을 수 있다

= 클럭을 더 높일 수 있다

= 성능을 더 높일 수 있다 정도로 이해하면 된다.

(물론 전압이 너무 높아 속도가 빠르면 그건 그거대로 문제가 된다. 클럭과 셋업/홀드 타임에 대해 검색해보면 나온다)

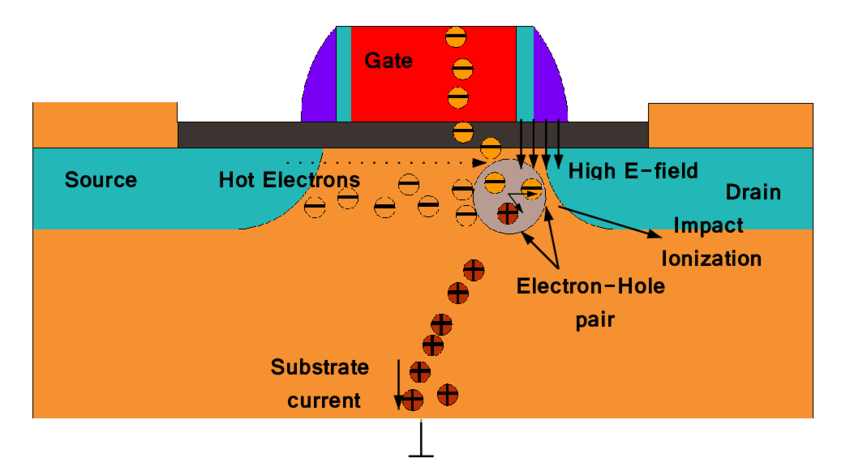

그런데 트랜지스터가 동작할 때, 고전압/고온 등 여타 이유로 캐리어가 가지는 에너지가 너무 강해질 경우, 본래라면 채널따라서 소스 - 드레인으로 가야하는 캐리어가 뜬금없이 게이트 쪽으로 튀어올라가거나, 멀쩡한 놈과 충돌해서 전자를 추가로 생성(Impact Ionization)하는 등, 여하튼 캐리어가 산화막(MOS에서 Oxide)에 갇히는 경우가 있다.

(아래 그림)

이렇게 산화물에 갇힌 캐리어들을 트랩(Trap)이라고 하는데, 말 그대로 함정이 되어서 채널 형성을 방해하는 역할을 한다.

이는 곧 문턱 전압 값이 높아지는 결과를 낳는다.

(산화막에 캐리어가 존재 => 게이트에 전압이 인가될 때 게이트 - 소스 간 전압 차이가 작아짐 => 문턱 전압 증가)

대충 스위치에 먼지 껴서 뻑뻑해진다고 이해하면 얼추 맞아 떨어진다.

위에서 말했지만 문턱 전압이 높아지면 같은 공급 전압 조건 하에서 트랜지스터의 속도가 떨어지고.

이는 곧 트랜지스터의 성능이 저하되는 것을 말한다.

이게 누적되면 결과적으로 이전과 같은 전압에서 동일한 성능으로 동작할 수 없게 되는 셈.

이러한 현상은 보통

1. 고온에서 전자가 가지는 에너지가 커질 경우(Hot Carrier Injection, HCI),

2. 고전압으로 강해진 전기장으로 전자가 가지는 에너지가 큰 경우(Negative Bias Tempereature Instability, NBTI)

등의 원인으로 발생한다.

반도체에서 고온 고전압을 피하는 이유 중 하나가 이러한 현상을 방지함에 있다.

2. 금속 선로 열화

중~고등학교 과학 지식으로는 회로의 금속 선로에는 저항이 존재하긴 하지만 그 값이 무시할 정도로 작기 때문에 무시하고 계산을 했을 것이고

실제로 충분히 두꺼운 금속 선로에 대해서는 이는 틀린 말이 아니다

그런데 위에서 말했듯 반도체 칩에 트랜지스터가 수 십 억개가 그 작은 공간에 치밀하게 들어가 있다.

회로를 구성하기 위해서 이 수많은 트랜지스터를 기능에 맞춰 선로를 구성하여 연결해야하고, 아무리 회로 최적화를 잘한다고 해도 궁극적으로 더 작은 공간에 더 많은 트랜지스터를 때려박기 위해서는 금속 선로의 두께를 줄일 수 밖에 없다.

실제로 첨단 공정에서 반도체 회로의 금속 선로의 단위 선폭/두께는 수십 ~ 수백 나노미터 단위에 지나지 않고, 인접한 금속 선로와의 거리도 이와 비슷하다.

이로 인해 금속 선로의 저항과 금속 선로 사이에서 생성되는 기생 커패시터는 절대로 무시할 수 없는 요소로 다가온다.

현재 반도체 설계하는데 선로 구성에 따라 셀 딜레이(트랜지스터 자체의 출력이 바뀔 때 소요되는 시간)보다 넷딜레이(신호가 금속 선로를 통과하면서 생기는 딜레이)가 큰 경우도 있는 마당이다.

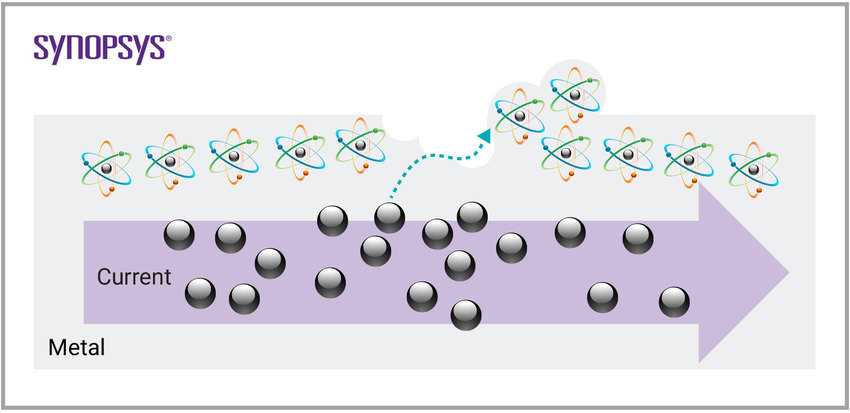

그런데 이때, 금속 선로를 전자가 통과하다보면 얘들이 얌전히 통과하면 좋은데 금속 원자들을 치고 지나간다

이 과정에서 금속 원자들의 배치가 변경되는데, 이를 전기전진(Elctromigration, 일렉트로마이그레이션, 이하 EM)이라고 한다

(아래 사진)

(대형 IP벤더/EDA 툴 제조사인 시높시스 사의 EM에 대한 아티클이니 관심 있으면 읽어보자

https://www.synopsys.com/glossary/what-is-electromigration.html )

이게 뭐 충분히 두꺼운 금속 선로면 원자 좀 이동된다고 문제가 생기지는 않겠지만

문제는 위에서 말했다시피 반도체 회로는 수십 ~ 수백 나노미터 단위의 금속 선로로 구성되어 있다

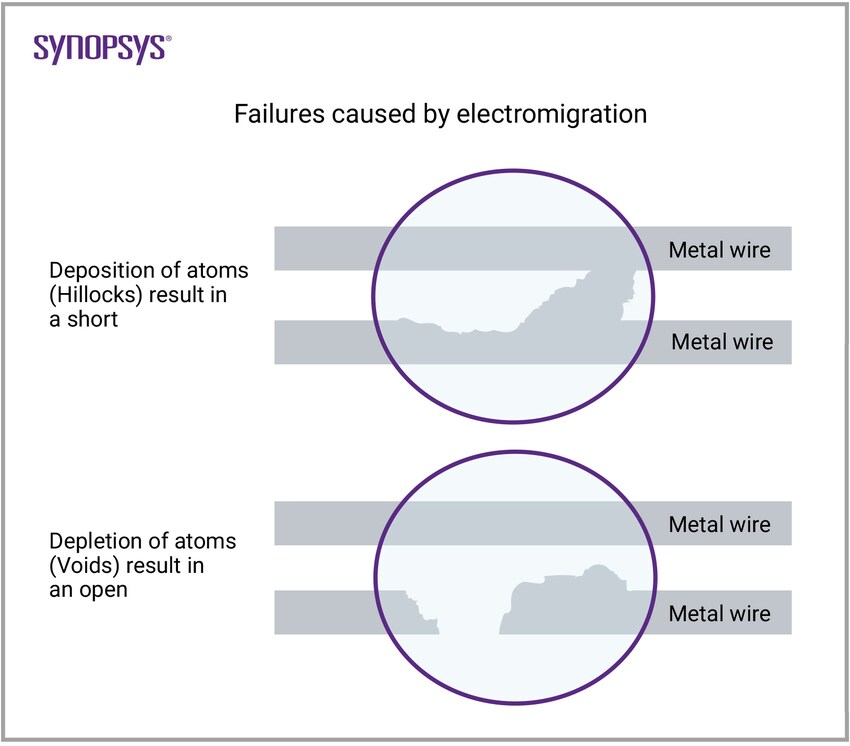

일렉트로마이그레이션으로 발생한 금속 선로의 두께가 변화하면서 금속 선로의 저항이 변경되고, 이로 인해 신호 전달 속도가 늦어질 수 있고,

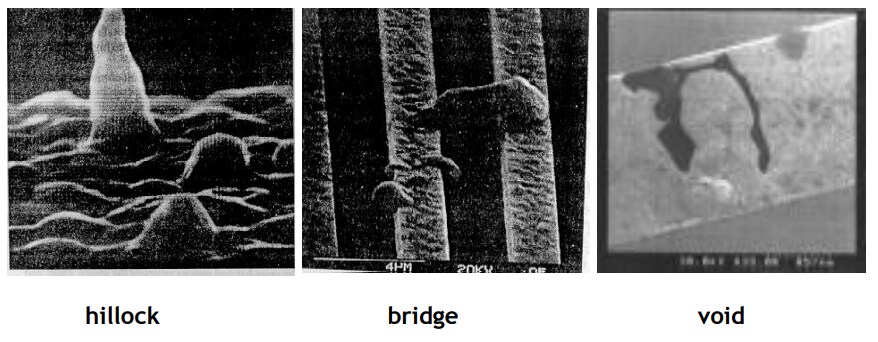

심한 경우 아래와 같이 아예 금속 선로가 끊기거나 인접한 금속 선로와 붙어버리는 경우도 존재한다.

또한, 단순히 신호를 전달하는 선로가 얇아져서 속도가 느려지는거나 오픈/쇼트가 발생해 오동작하는 것만 문제가 아니다.

반도체 회로를 구성할 때 중요한 것 중 하나가 트랜지스터에 어떻게 전원을 잘 공급하느냐인데, EM은 이에도 영향을 끼친다.

금속 선로의 저항이 변화하면 같은 전압을 바깥에서 공급하더라도, 금속 선로를 지나가며 전압이 떨어져서 트랜지스터에 공급되는 전압이 감소하여 트랜지스터 자체의 속도까지 느려질 수 있고,

최악의 경우 신호 선로와 마찬가지로 전원 선로가 저들끼리 붙거나 끊어지면서 트랜지스터에 전압이 비정상적으로 공급되는 경우도 발생할 수 있다.

(이러한 전원 공급을 위한 금속 선로의 구성을 power grid, power mesh 등으로 부르는데, 이 power grid/mesh의 저항으로 인해 손실되는 전압을 IR Drop이라고 하며 반도체 설계 시 신경 쓰는 부분 중 하나이다)

여담으로 이런 신뢰성에 관한 내용을 설계 시 시뮬레이션 등을 통해 검증하게 되는데, 이 때 칩의 동작 환경에 따라 검증 조건이 달라진다.

예를 들자면, 비교적 교체 주기가 짧고 계속 동작하지만 동작 온도가 그리 크지 않은 모바일 칩셋의 경우 5년에 85도 정도 조건으로 장기간 동작하는 걸 기준으로 보고,

교체 주기가 길지만 가동 시간이 짧고 온도가 높은 차량은 3년에 125도 조건으로 보는 등 차등을 둔다.

(실제로는 파운드리 업체마다 다른 것으로 알고 있음)

물론 실제 설계 시에 이러한 사항을 감안하고 충분한 마진을 두고 설계하고,

기준이 일반적인 사용 조건보다 좀 더 가혹한 조건이기 때문에 하드코어하게 갈구지 않는 이상 일반 사용자가 체감할 일은 별로 없다고 보면 된다

(IP보기클릭)126.241.***.***

(IP보기클릭)121.183.***.***

야쨜 달리다 짤릴거 같으니 이상한걸로 바꿔버리네 빨리 원복시켜라

(IP보기클릭)211.234.***.***

(IP보기클릭)121.169.***.***

전압보다는 전류의 문제 = 얼마나 많은 전자가 그 선로를 타고 이동했는가 그 어느 실험인지는 기억 안나는데 전자가 아주아주 낮은 확률로 원자핵 치고 지나가면 설명된다는 실험 있었잖아 그게 확장된거라고 보면 됨 전류가 지속적으로 흐른다 = 전자의 이동 횟수가 많다 = 어쩌다 얻어 걸리는 원자핵과 충돌 횟수가 많아진다 | 24.05.15 17:02 | | |

(IP보기클릭)110.76.***.***

러더퍼드 원자핵 입증실험? 좀 느낌은 다른거 같지만 애당초 전자랑 핵이랑 충돌에서 전자쪽 에너지량은 큰 의미가 없는거려나 땡큐땡큐 | 24.05.15 17:06 | | |