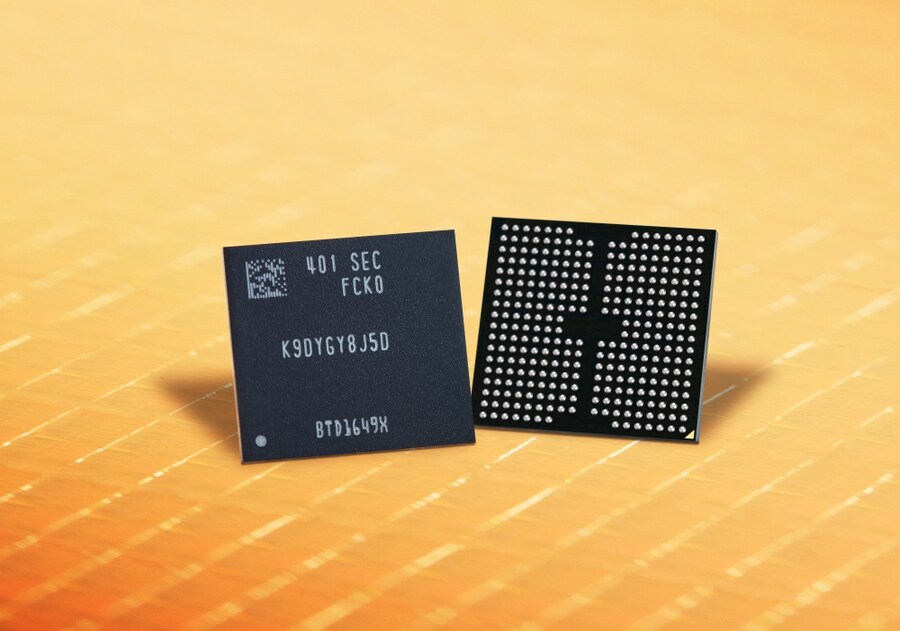

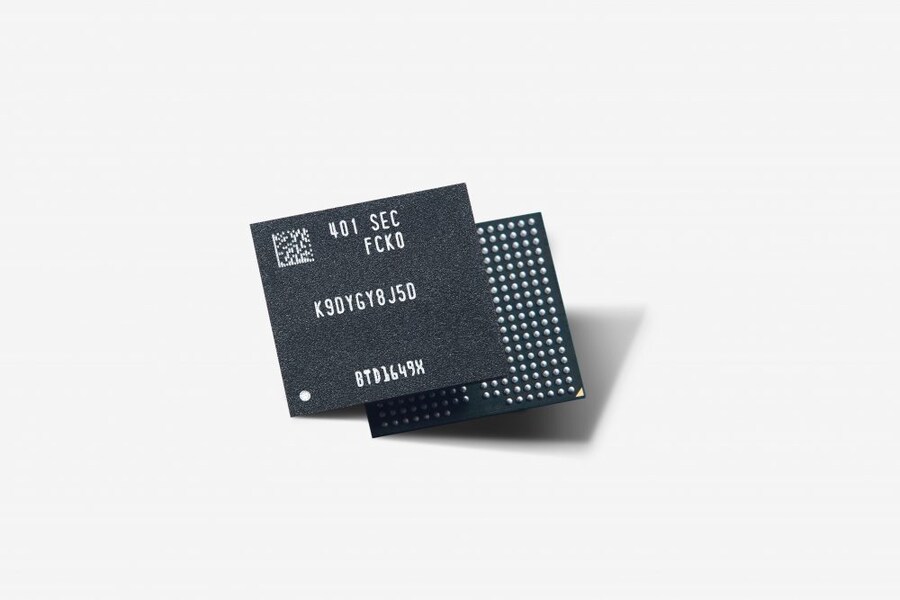

삼성전자가 업계 최초로 ‘1Tb(테라비트) TLC(Triple Level Cell) 9세대 V낸드’ 양산을 시작하며 낸드플래시 시장에서의 리더십을 공고히 했다.

삼성전자는 ▲업계 최소 크기 셀(Cell) ▲최소 몰드(Mold) 두께를 구현해 ‘1Tb TLC 9세대 V낸드’의 비트 밀도(Bit Density)를 이전 세대 대비 약 1.5배 증가시켰다.

* 비트 밀도(Bit density): 단위 면적당 저장되는 비트(Bit)의 수

더미 채널 홀(Dummy Channel Hole)제거 기술로 셀의 평면적을 줄였으며, 셀의 크기를 줄이면서 생기는 간섭 현상을 제어하기 위해 셀 간섭 회피 기술, 셀 수명 연장 기술을 적용해 제품 품질과 신뢰성을 높였다.

* 더미 채널 홀 (Dummy Channel hole): Cell Array에서 Plane을 구분하기 위해 만들어진 동작을 수행하지 않는 채널 홀

삼성전자의 ‘9세대 V낸드’는 더블 스택(Double Stack) 구조로 구현할 수 있는 최고 단수 제품으로, ‘채널 홀 에칭(Channel Hole Etching)’ 기술을 통해 한번에 업계 최대 단수를 뚫는 공정 혁신을 이뤄 생산성 또한 향상됐다.

‘채널 홀 에칭’이란 몰드층을 순차적으로 적층한 다음 한번에 전자가 이동하는 홀(채널 홀)을 만드는 기술이다. 특히, 적층 단수가 높아져 한번에 많이 뚫을수록 생산효율 또한 증가하기 때문에 정교화∙고도화가 요구된다.

‘9세대 V낸드’는 차세대 낸드플래시 인터페이스인 ‘Toggle 5.1’이 적용돼 8세대 V낸드 대비 33% 향상된 최대 3.2Gbps의 데이터 입출력 속도를 구현했다. 삼성전자는 이를 기반으로 PCIe 5.0 인터페이스를 지원하고 고성능 SSD 시장을 확대해 낸드플래시 기술 리더십을 공고히 할 계획이다.

또 ‘9세대 V낸드’는 저전력 설계 기술을 탑재하여 이전 세대 제품 대비 소비 전력이 약 10% 개선됐다. 환경 경영을 강화하면서 에너지 비용 절감에 집중하는 고객들에게 최적의 솔루션이 될 것으로 기대된다.

삼성전자는 ‘TLC 9세대 V낸드’에 이어 올 하반기 ‘QLC(Quad Level Cell) 9세대 V낸드’도 양산할 예정으로 AI시대에 요구되는 고용량∙고성능 낸드플래시 개발에 박차를 가할 계획이다.

(IP보기클릭)118.235.***.***

양산전자 간만에 함 가보자

(IP보기클릭)118.235.***.***

양산전자 간만에 함 가보자

(IP보기클릭)59.5.***.***

(IP보기클릭)58.231.***.***

삼성이 원래 3D NAND 원조 집이고 Stack 없이 236단까지 했었는데 이번에 Double Stack 가면서 한 번에 키옥시아나 하이닉스 보다 높은 단수 양산하는 거 | 24.04.25 17:55 | | |

(IP보기클릭)119.197.***.***