한국 IBM 유부선 차장

1. 프로세서 시장 Overview

최근 세계 프로세서 시장은 급격한 변동을 경험하고 있다. 90년대 중반까지만 해도, MIPS나 Alpha 등 다양한 아키텍춰의 프로세서들이 군웅할거하고 있었으나, 2000년대 초반에 들어오면서 흡수 합병 및 시장에서의 도태 등을 통해, 주목할 만한 프로세서 아키텍춰는 다섯 손가락으로 셀 수 있을 정도만 남게 되었다.

특히 작년에는 Intel이 Itanium2 프로세서를 출시했고, AMD에서도 x86-64 아키텍춰의 Opteron 프로세서를 출시, Intel에 정면 도전하여 좋은 성과를 거두었으며, 올해 6월에는 Sun이 2006년 새롭게 출시될 새로운 서버 제품군에 후지쯔가 개발 중인 SPARC64VI 프로세서를 탑재하겠다고 발표하는 등, 많은 변화가 있었다. 가장 최근의 일로는, IBM이 그 동안 약속해온 세계 최정상급의 POWER5 processor를 약속대로 시장에 내놓은 일이 될 것이다.

이러한 프로세서 시장, 특히 서버 프로세서 시장에 지각변동이 일어나고 있는 것은, 크게 보았을 때, 다음과 같은 요인에 의한 것이라고 볼 수 있다.

1) 파이

닷컴 버블의 붕괴 이후 이어진 IT 업계의 장기 저성장으로 인해, 업계간의 경쟁이 파이 키우기(시장 전체의 성장)에서 파이 빼앗기(한정된 시장에서의 점유율 경쟁) 국면으로 돌아섰다. 이 과정에서, 경쟁력 개선에 성과를 보이지 못한 업체는 도태될 수 밖에 없었다.

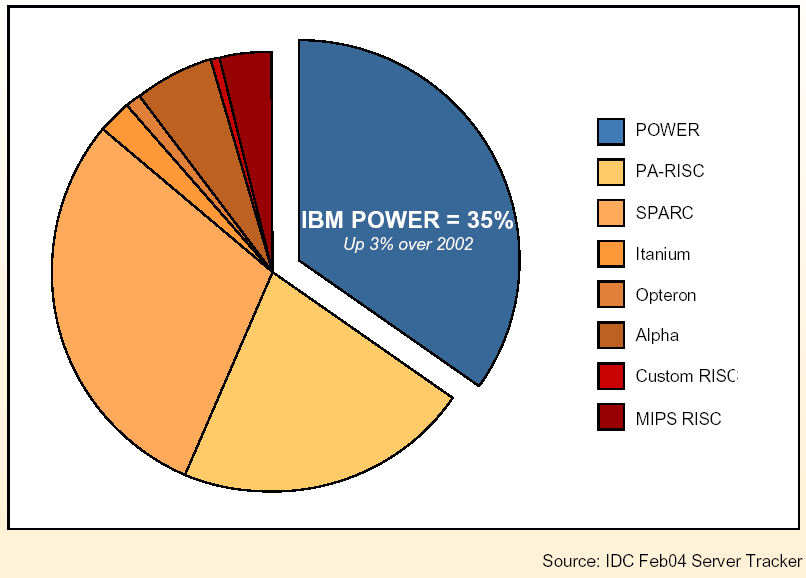

2) 64-bit

제자리를 맴도는 매출액과는 별도로, IT 기술의 빠른 향상은 더욱 큰 성능과 확장성을 요구한다. 이는 필연적으로 64-bit 컴퓨팅의 일반화를 뜻한다. 기업용 UNIX 시장에서는 이미 64-bit가 일반화 되었지만, 가장 많은 수의 processor를 생산하는 Intel에게는 이야기가 다르다. 특히, 데스크탑 PC 시장이 포화 상태에 이른 지금, 엔터프라이즈급 서버 시장에의 진입이 절실한 Intel은 새로운 64-bit 아키텍춰의 개발과 그 성공에 사운을 걸었다고 해도 지나치지 않은 중대성을 부여하고 있다. (그림 1. 참조)

3) 규모

경쟁이 치열해지면서, 성능은 물론 가격 면에서의 경쟁력이 점점 더 의미를 갖게 되었고, HP나 Sun처럼 서버 사업에 재정적인 어려움을 겪던 기업체들은 규모의 경제를 위해 투자 개발 파트너를 찾을 수 밖에 없는 상황이 되었다.

그림 1. 2003년 64-bit 아키텍춰 매출액

이러한 상황 속에서, 가장 주목받고 있는 두 아키텍춰를 택하라고 한다면, 역시 IBM의 POWER와 Intel의 EPIC(Itanium) 아키텍춰를 들 수 있다. 이 두 아키텍춰는 그 성능이나 규모, 기술력에 있어서 단연 두각을 보이고 있기 때문이다. 그 중 조용히, 그러나 확고하게 업계의 혁신적 표준으로 자리잡고 있는 POWER 아키텍춰에 대해 알아보도록 하겠다.

2. 역사

IBM POWER는, 1970년대 IBM에서 최초로 RISC의 개념이 발명되면서 시작되었다고 할 수 있다. 최초의 POWER 제품군이 1990년에 출시된 이래, IBM은 Apple, Motorola와 합작으로 개발한 PowerPC 아키텍춰와 함께 POWER 아키텍춰를 꾸준히 발전시켜오고 있다.

다음은 IBM POWER 아키텍춰의 간략한 역사이다.

- 1974년, IBM의 John Cocke가 RISC를 발명.

- 1980년, IBM이 최초의 RISC architecture를 응용한 prototype computer 개발

- 1990년, IBM이 새로운 RISC 기반 computer 제품군, 즉, RS/6000 발표. 이 system의 architecture가 Performance Optimization With Enhanced RISC (POWER).

- 1991년, POWER 기반의 새로운 PowerPC processor를 개발하여 PC와 low-end workstation에 적용하기로 IBM, Apple, Motorola가 협약

- 1993년, Scalable POWERparallel system, 즉 RS/6000 기술을 이용한 최초의 microprocessor 기반의 supercomputer 발표.

- 1994년, Scalable POWERparallel Systems 2 (SP2) 발표.

POWER 아키텍춰에 기반한 최초의 임베디드 제어기인 PowerPC 403GA를 발표

- 1995년, PowerPC 64-bit processor

- 1996년, 32-bit, 135MHz POWER2 SuperChip (P2SC)을 발표.

- 1997년, IBM의 POWER 기반 수퍼컴퓨터인 Deep Blue가 세계 Chess 챔피언인 Garry Kasparov에게 승리.

IBM이 NASA의 화성 탐사선 Pathfinder에 PowerPC microprocessor를 공급.

- 1998년, 332MHz PowerPC 604 기반의 supercomputer Blue Pacific을 IBM과 미 에너지성 Lawrence Livermore 국립 연구소이 공동 개발.

IBM이 최초의 구리칩 기반의 PowerPC 740/750 출시

POWER2 architecture (P2SC)와 PowerPC architecture를 POWER3로 통합.

IBM이 최초의 임베드된 POWER 기반의 SOC (System on Chip)인 PowerPC를 구체화.

- IBM이 405 core에 기반한 최초의 SOC (System on Chip)인 PowerPC 405GP를 발표.

IBM과 Nintendo가 차기 가정용 게임기인 GAMECUBE에 PowerPC 기반의 chip을 사용하기로 10억불 상당의 다년간 계약을 발표.

- IBM이 POWER 기반의 서버 제품군 명칭을 RS/6000에서 pSeries로 개명

- 2001년, Lawrence Livermore 국립 연구소에서, IBM의 supercomputer인 ASCI White (Accelerated Strategic Computing Initiative, 가속 전략 컴퓨팅 계획)를 핵폭발 효과의 연구를 위해 사용 개시.

IBM이 세계 최강의 UNIX 서버인 POWER4 기반의 eServer p690을 발표.

Sony Computer Entertainment와 IBM, 그리고 Toshiba가 광대역폭 시대를 이끌 새로운 진보된 칩 아키텍춰(코드명 “Cell”)를 연구 개발하기로 합의.

- 2002년, POWER4 아키텍춰에 기반을 둔 PowerPC 970을 발표.

IBM이 세계 최고의 진보된 기술 설비를 갖춘 300 mm 반도체 설비를 개설. IBM의 “foundry” 제조 서비스는 물론, 주문형 및 표준 chip 제공 능력을 증대.

IBM이 주로 embedded networking 및 storage 장치에 사용할 PowerPC 440GP와 440GX embedded processor를 출시.

- 2003년, IBM이 32-bit embedded PowerPC microprocessor core에 대한 공개 라이센스 프로그램을 발표.

Apple과 IBM이 세계 최초의 64-bit desktop processor인 PowerPC G5를 발표.

IBM이 64-bit PowerPC를 장착한 BladeCenter JS20을 발표.

- 2004년, IBM이 업계 최초로, silicon-on-insulator (SOI)와 인장 silicon 및 구리 배선 기술을 조합하여 저전력 고성능 microprocessor를 생산하는 새로운 제조 기술을 개발 사실을 발표.

POWER5 발표.

3. 기술 개요(POWER vs, Itanium or RISC vs CISC)

먼저, POWER 아키텍춰의 기본적인 설계부터 보도록 하자. IBM POWER 아키텍춰에는 RISC 아키텍춰의 전형적인 특징이 구현되어 있다. 각각의 instruction은 일관성있는 포맷의 4-byte 고정 길이로 되어 있어, instruction decoding 기구가 단순화되도록 했다. 한 세트의 범용 레지스터(General Purpose Register, GPR)가 고정 소수점 연산과 memeory access 연산을 담당하도록 되어 있고, 유동 소수점 연산을 위해서는 따로 한 세트의 유동 소수점 레지스터(Floating-Point Register)를 제공한다. 모든 연산은 하나의 레지스터 세트에서 원천 연산자를 가져와서 연산 결과를 같은 레지스터 세트에 저장한다.

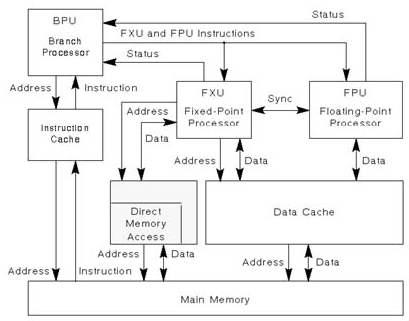

POWER 아키텍춰가 다른 RISC 아키텍춰와 구별되는 특장점은, 프로그램 흐름 제어와 고정 소수점 연산, 유동 소수점 연산 기능이 각각 기능적으로 분할되어 있다는 점이다. 이 분할로 인해, 독립적 instruction 여러 개를 한꺼번에 여러 개의 기능 요소를 이용해 실행할 수 있는 수퍼스칼라(superscalar) 설계가 용이해졌다. (그림 2. 참조)

BPU – Instruction을 가져오고 (fetch), branch 및 CR instruction을 실행하고, FXU 및 FPU instruction을 dispatch한다.

FXU – 고정 소수점 instruction을 실행하고 유동 소수점 로드의 주소를 계산하고 저장한다.

FPU – 유동 소수점 instruction을 실행하고 유동 소수점 로드의 data를 관리하고 저장한다.

그림 2. POWER 및 PowerPC 아키텍춰

이렇게 다른 RISC 아키텍춰와 다른 방향을 취한 것은, 전체적인 성능의 증가를 위해서이다. 즉, 다른 RISC 아키텍춰들은 가능한한 빠른 속도로 instruction을 실행하는 것에만, 다시 말해 cycle 시간을 줄이는 것에만 중점을 두는 것에 비해, POWER 아키텍춰는 주어진 업무를 끝마치는데 드는 전체 시간을 최소화 하는 것에 역점을 두었다. 여기서, 전체 시간이란 경로 길이, instruction 완료에 필요한 cycle의 수, 그리고 cycle 시간의 곱으로 주어진다.

대개의 프로그램에서, instruction들의 20~30%는 로드와 저장이 차지한다. 또한, 많은 프로그램에서는 일정한 메모리 접근 방식을 가지는 배열을 다루게 된다. 이 점에 착안하여, POWER 아키텍춰에는 대개의 로드 및 저장 instruction에 갱신 형태를 포함시켜, 하나하나의 메모리 접근 뒤에 별도의 주소 연산이 필요하지 않도록 했다.

POWER 아키텍춰를 처음 접하는 사람은, POWER와 PowerPC라는 두가지 이름의 아키텍춰에 대해 혼란을 느낄 수도 있다. 이는 1991년의 Apple, Motorola, IBM의 협약의 결과이며, 결론적으로 말해, 두 아키텍춰는 한가지에서 나온 것이라고 할 수 있다. 그 배경은 다음과 같다.

기업용 컴퓨터 시장에 있어서, 성능이 가장 중요한 것은 아니다. 중요한 것은 기업의 생산성 향상과 비용 절감인데, 이는 컴퓨터 시스템이 얼마나 다양한 업무를 수행할 수 있는가와 직결되어 있다. 즉, 해당 시스템에서 수행할 수 있는 업무 애플리케이션의 다양성이 매우 중요한 것이다.

1990년에, 5개의 RISC 아키텍춰가 시장 점유율을 다투고 있었는데, 이는 너무 많은 숫자였다. 한 애플리케이션에 대해 개발자들이 UNIX에 대해서만 5개의 버전을 내놓아야 한다면 이는 지나친 부담이었다.

이러한 시장 상황에 효율적으로 대처하기 위해, 1991년, Apple과 Motorola, IBM이 POWER 아키텍춰에 근거한 새로운 아키텍춰를 개발하기로 했다. 이것이 PowerPC 아키텍춰이고, 다음과 같은 목표를 가지고 개발을 시작했다.

- 저가의 제어기부터, 고성능 processor까지 다양한 범위에서 구현될 수 있도록 한다.

- Cycle 시간이 짧아지도록 단순한 구조를 갖는 설계를 한다.

- 적극적인 수퍼스칼라의 구현을 저해하는 요소를 최소화한다.

- 멀티프로세서 기능을 포함한다.

- 32-bit 아키텍춰의 연장선상에서 64-bit 아키텍춰를 정의하여, 32-bit 애플리케이션에 대해 이진 호환성을 제공한다.

PowerPC 아키텍춰에는 기존 POWER instruction의 대부분을 포함하고 있다. 또 제외된 instruction은 거의 사용되지 않는 것 중 compiler가 기존의 다른 instruction으로 대체할 수 있는 것들이 거의 대부분이다. 여기에서도 제외된 극소수의 instruction은, AIX 운영체제에서 에뮬레이션을 해주므로, 기존의 POWER용 애플리케이션을 그대로 PowerPC에서 수행할 수 있다.

PowerPC 아키텍춰는 64-bit 기반으로서, 메모리 주소와 고정 소수점 연산이 64-bit로 연장되고, 64-bit 모드와 32-bit 모드 간의 동적 변환을 지원한다. 32-bit 모드에서는, 32-bit 아키텍춰에서 컴파일된 애플리케이션을 64-bit processor에서 수행할 수 있다.

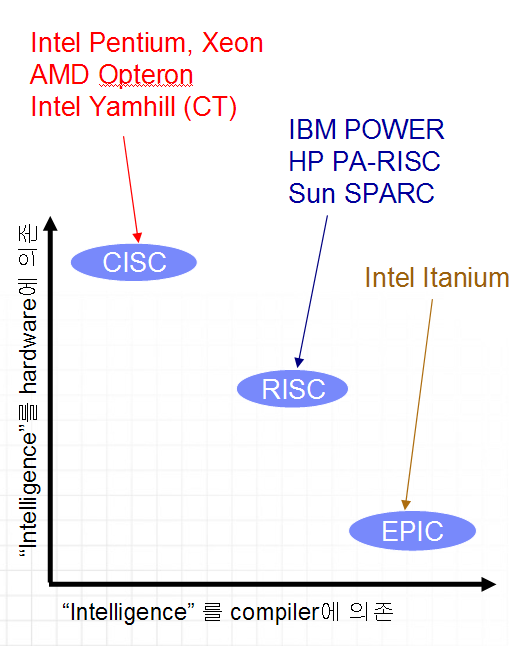

RISC 계열로서의 POWER 아키텍춰를 다른 계열의 프로세서와 비교해보면, CISC (Complex Instruction Set Computing) 계열이나 EPIC (Explicitly Parallel Instruction Computing) 계열에 비해, 하드웨어 및 컴파일러의 기능을 균형있게 사용하는 것을 볼 수 있다. (그림 3. 참조)

그림 3. 프로세서 아키텍춰 계열간 비교

특히, 이 특징은 EPIC 계열인 인텔 Itanium 프로세서와 비교할 때 두드러진다. Itanium은 컴파일러에 과도하게 의존하여 스케쥴링이 정적이고, 컴파일러에 의한 공격적인 speculation (저장되지 않은 data를 미리 memory에 끌어옴으로써 memory latency를 줄이는 기법)이나 branch predication (조건문을 만나 병렬처리가 불가능할 때, 조건문의 양쪽 흐름을 모두 연산하고 나서 나중에 맞는 흐름의 값만을 취하는 기법) 등의 기법을 사용한다. 그 결과, 일부 성능 개선이 있을 수도 있지만, 예외 현상이 발생할 경우 오히려 성능이 떨어질 수도 있고, 이 모든 처리가 컴파일러에 의해 처리되므로 동적으로 일어나는 상황에 대처하지 못하고 코드 프로파일링을 거쳐 최적화를 해야만 한다. 무엇보다도, 하드웨어 자원을 과다하게 사용하므로, 같은 크기의 캐쉬를 장착한 경우 RISC 계열보다 성능이 떨어지게 된다는 단점이 있다.

이에 비해, POWER는 고전적인 비순차 실행 (out-of-order execution) 및 branch prediction (조건문을 만나 병렬처리가 불가능할 때, 프로그램의 기존 거동으로부터 어느 흐름이 선택될 지 예측하여 그 흐름을 계산하는 기법)을 사용한다. 특히 이러한 처리는 하드웨어적으로 처리되므로, 동적인 처리가 가능하다.

POWER와 Itanium의 비교는 표 1.을 참조하기 바란다.

|

|

POWER |

Itanium |

|

Branch Prediction |

Yes |

Yes |

|

Branch Hints |

Yes |

Yes |

|

Branch Predication |

No |

Yes |

|

Instructions / 16 Bytes |

4 |

3 |

|

Data Prefetch |

Yes, SW가 보조하는 HW 기능에 의해 |

Yes, explicit SW 제어에 의해 |

|

Instruction Prefetch |

Yes, HW 제어에 의해 |

Yes, SW 제어에 의해 |

|

Control Speculation |

Yes, HW의 out-of-order execution에 의해 |

Yes, explicit instruction 및 SW check에 의해 |

|

Data Speculation |

Yes, HW의 out-of-order execution에 의해 |

Yes, explicit instruction 및 SW check에 의해 |

|

Loop Unrolling |

Compiler 및 HW의 out-of-order execution에 의해 |

Compiler에 의해 |

|

Hardware |

동적 scheduling |

정적 scheduling, 즉, compiler가 지시한 대로만 수행 |

표 1. POWER와 Itanium 비교표

POWER 아키텍춰의 특징 중의 하나는 저전력 설계이다. 이는 진보된 RISC 설계 기술과 IBM만이 가진 칩 제조 기술, 즉, 구리 배선이나 SOI (Silicon-On-Insulator) 등이 결합한 결과이다. 실제로, POWER 기반의 IBM pSeries는 PowerPC 프로세서를 사용할 때부터도, 경쟁사에 비해 낮은 clock speed로도 더 뛰어난 성능을 내었고, 그 결과 냉각 팬 소리가 조용한 서버로 유명했다. 이러한 저전력 특징은, 서버를 위한 인터넷 데이터 센터 등의 유지 비용과도 직결되지만, 특히 임베디드 장치에 사용될 때 매우 중요한 역할을 한다. 이러한 저전력 설계는 POWER5에 이르러 동적 전력 관리 기능이 추가되면서 더 두각을 보이게 될 것이다.

POWER4부터, POWER 아키텍춰에는 두드러진 특징, 즉, 하나의 칩 위에 두개의 프로세서 코어가 장착된 SOC (System On Chip) 개념이 도입된다. 이는 IBM이 1998년부터 구체화해온 전략적이고 혁신적인 개념으로서, 하나의 칩을 마치 하나의 SMP 시스템처럼 구성하여, 프로세서간의 고속통신 및 데이터 공유에 있어 획기적인 향상을 이루어낸 개념이다. (그림 4. 참조)

그림 4. POWER4 듀얼 코어 아키텍춰

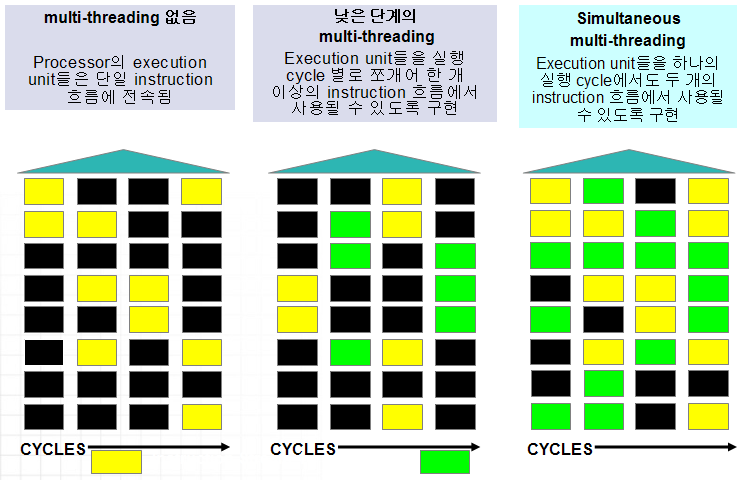

POWER5에서 구현되는 새로운 특장점 중 가장 두드러지는 것은 SMT(Simultaneous Multi-Threading, 동시 멀티쓰레딩)과 마이크로 파티셔닝(micro-partitioning)이다.

SMT는 간단히 말해, 하나의 프로세서가 2개의 데이터 쓰레드를 처리하도록 해주는 기능이다. 기존의 프로세서에서도 멜티쓰레딩이 가능했지만, 사실 그것은 하나의 시간대(tick, time slice)에서는 하나의 쓰레드만을 처리하는 것이었다. 그러나, SMT를 구현하게 되면, 하나의 시간대에서 두개의 쓰레드를 동시에 처리할 수 있게 되어, 논리적으로는 두개의 프로세서가 있는 것과 같은 효과를 볼 수 있게 된다. 예전의 기술로는, 프로세서에 장착된 실행 유닛들을 불과 20~25%만을 사용할 수 있었으나, 이 SMT로 인해 그 활용도를 크게 높일 수 있게 되었다. (그림 5. 참조)

그림 5. SMT (Simultaneous Multi-Threading)

마이크로 파티셔닝은 하나의 POWER5 프로세서 코어를 10개까지 파티셔닝 함으로써, 기존의 LPAR (논리적 파티셔닝) 기능을 한층 더 발전시킨 것이다. 이는 IBM의 메인프레임에서나 가능하던 기술로서, 시스템 자원 활용을 극대화하는 것에 필수적인 기술이며, 하드웨어적인 보드/셀 단위의 조악한 파티셔닝만 가능한 경쟁사와는 확연히 기술력의 차이를 보여주는 부분이라고 할 수 있다.

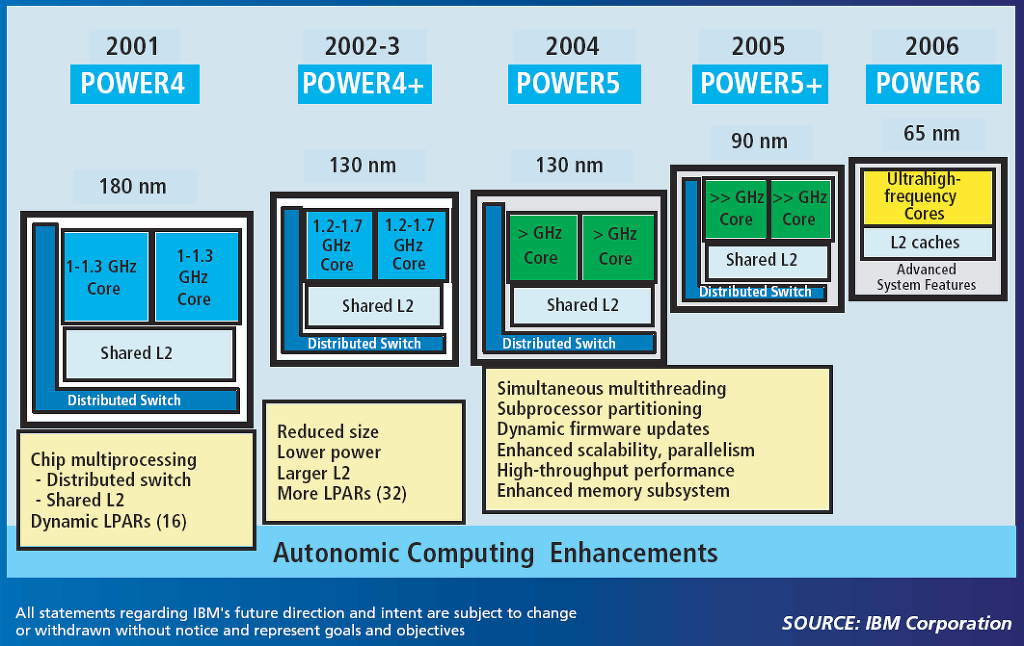

4. 로드맵

IBM은 자사가 제시한 로드맵을 충실하게 잘 이행해온 것으로 명성이 높다. 이번에도 POWER5 프로세서를 약속에 맞추어 시장에 선보였다. 이는 연필로 자사의 로드맵을 그리고 있는 (즉, 언제든지 지우고 다시 그릴 준비를 하고 있는) Sun이나 HP와는 확연히 대비되는 점이다. 가령 Sun은 야심차게 추진했던 dual core 프로세서인 UltraSPARC V와 Gemini를 포기한다고 올해 4월에 발표하였다. 그 이유는 재정적인 부담 때문이었다. 또한 HP는 Itanium에 사운을 걸고 PA-RISC 프로세서는 개발을 중단할 것처럼 내비치다가, 최근 들어 Itanium의 시장 전망이 모호해지면서, PA-RISC 8900까지의 로드맵을 다시 강조하면서 AMD의 Opteron 프로세서를 탑재한 서버를 출시하는 등 혼란스런 모습을 보이고 있다.

IBM은 경쟁사들이 갖추지 못한 결정적인 것, 즉 진보된 마이크로프로세서 제조 공정을 가지고 있다는 것을 로드맵을 통해서 과시하고 있다. 기업 비밀상 아직 POWER5+나 POWER6에서 어떤 특장점을 보여줄지에 대해서는 발표하고 있지 않지만, clock speed의 증대와 칩 다이의 크기 축소 등을 통해 구리 배선, SOI (Silicon-On-Insulator), 저-k 유전체 (low-k dielectric), 인장 실리콘 (strained silicon) 등의 기술력을 보여주고 있다. (그림 6. 참조)

그림 6. IBM POWER 프로세서 로드맵

또한 IBM은 POWER 아키텍춰 자체의 저변 확대를 위해 전략적으로 노력해오고 있다. POWER는 중대형 서버에 장착되는 프로세서 아키텍춰라고 일반적으로 알려져 있지만, 사실은 꼭 그렇지 않다. IBM POWER는 자동차 제어장치, GPS 등 임베디드 장치부터 시작하여 대형 pSeries 서버에 이르기까지 전체 산업계에 사용되는 범용 아키텍춰이다. 가령, 대표적인 PowerPC 라이센스 업체 중 하나인 Motorolar는 휴대폰, 자동차, GPS 등의 디지털 신호 처리에 POWER 기술을 사용하고 있으며, 저장장치 업체인 EMC에서는 그 회사의 대표적 저장 장치 제품인 Symmetrix disk controller에 POWER 기술을 사용했다. 또한, Nintendo의 차세대 게임 콘솔인 GameCube, Sony의 PlayStation2, Microsoft의 Xbox 차기 모델 등 가정용 기기에도 POWER 기술이 사용되고 있다.

이는 IBM의 오래된 전략적 노력 중 결정적인 부분이다. HP의 Itanium/Windows 전략이나 Sun의 UltraSPARC/Solaris 전략과는 달리, IBM은 다양한 운영 환경을 위한 기업 컴퓨팅 솔류션의 제공자가 되기 위한 노력을 해왔다. IBM은 독자적인 OS인 AIX나 i5/OS 외에도, Linux 및 iSeries 솔루션 상의 Windows처럼 다양한 솔루션을 제공하고 있으며, 특히 POWER와 Linux를 결합하여, 소형 워크스테이션부터 블레이드 환경 및 대형 서버군에 이르기까지, 상업용 애플리케이션은 물론, HPC 및 GRID를 위한 범용 32-bit 및 64-bit 환경을 제공한다.

IBM은 올해부터 “POWER Everywhere”라는 구호를 앞세우고, POWER 저변 확대에 적극적으로 나서고 있다. 올해 초 POWER 아키텍춰 자체를 오픈 소프트웨어처럼 협력사와 개발자 등에게 공개하기로 결정한 것이 그 대표적인 예이다.

IBM은 주문형 chip과 ASIC을 공급하고 있는데, 이들은 POWER 아키텍춰의 필수적인 구성 요소이다. IBM은 협력사들이 설계 단계부터 시작하여 임베드된 메모리, 피키지, 코어 및 완성형 제품에 이르기까지 ASIC을 만들 수 있도록 도와주고 있으며, 독립업체들이 프로세서 및 네트워크, 소비자 제품 등에 대한 지적 재산권을 창조하고 소유할 수 있도록 해주고 있다. 사실, 이들 ASIC 중 많은 수에 POWER 코어가 사용되고 있다. IBM이 프로세서 코어 부분의 표준 기능을 성능 등에 대해 최적화해놓았기 때문에, 협력사는 그 위에 부가될 독특한 가치와 그를 이용한 혁신적 제품 개발에만 전념할 수 있다.

5. 결론

일반적으로, 프로세서라고 하면 인텔 프로세서가 가장 널리 알려져 있고, 마치 산업계의 표준인 것처럼 알고 있는 사람조차도 있다. 그러나, 인텔은 가장 널리 사용되는 데스크탑 PC 및 소형 32-bit 서버에 가장 많이 사용되는 프로세서를 생산할 뿐이다. 64-bit 컴퓨팅에 있어서, 인텔은 EPIC이라고 하는 아직 검증되지 않은 전혀 생소한 아키텍춰를 이용하여 이제 겨우 시작하는 후발 주자일 뿐이며, 그 주력 제품인 Itanium 프로세서의 전망은 그리 밝아 보이지는 않는다.

POWER 아키텍춰야 말로, 임베디드 장치부터 엔터프라이즈급 서버에 이르기까지 일관적으로 사용되는 범용 아키텍춰이며, 이미 많은 곳에서 검증을 거쳤고, Sony나 Toshiba, Apple 등과 같은 협력사들과 함께 더욱 진보된 미래를 약속하고 있다. 무엇보다도, 연속적으로 세계 특허 1위를 달리고 있는 IBM의 앞선 기술력을 바탕으로, POWER 아키텍춰는 앞으로도 혁신적 표준으로서의 가치를 굳히게 될 것이다.

http://www.ibm.com/kr/kugchan (클릭)

(IP보기클릭).***.***

'POWER 아키텍춰는 앞으로도 혁신적 표준으로서의 가치를 굳히게 될 것이다.' 현실은 협력사들이 버리거나 협력사가 망하거나...

(IP보기클릭).***.***

리포트로 제출해도 되겠네

(IP보기클릭).***.***

Wii x 3 = Wii U

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***

리포트로 제출해도 되겠네

(IP보기클릭).***.***

'POWER 아키텍춰는 앞으로도 혁신적 표준으로서의 가치를 굳히게 될 것이다.' 현실은 협력사들이 버리거나 협력사가 망하거나...

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***

Wii x 3 = Wii U

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***

(IP보기클릭).***.***