인텔의 10나노 공정이 지지부진한 가운데 삼성과 TSMC는 7나노 공정 양산을 시작했습니다 그렇다면 다음은 5나노 공정입니다.

TSMC가 5나노 공정 주요 지표를 공개했습니다.

TSMC는 내년 2세대 7나노 공정의 일부 중요하지 않은 레이어는 EUV 공정을 최초로 도입한다고 합니다. 노드 명칭은CLN7FF에서 CLN7FF+가 됩니다.

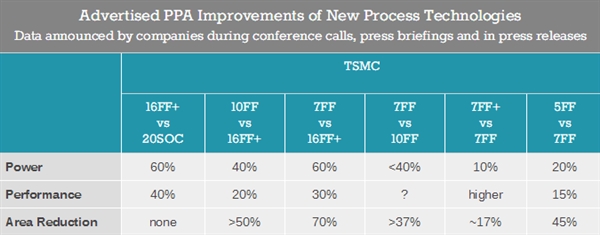

트렌지스터 밀도가 20퍼센트 향상되고 동일밀도/클럭에서 전력사용량 10퍼센트가 절감됩니다.

TSMC 5나노 공정은 계속해서 ASML Twinscan NXE:3400을 사용해서 처리합니다 EUV 적용 범위를 넓히면서 7나노 대비 밀도가 80퍼센트가 늘어납니다.

이렇게 보면 좋아보이지만 문제는 실 클럭 향상은 15퍼센트에 그친다는겁니다 동일클럭/밀도에서 소비전력 감소도 20퍼센트 정도

현재 EUV 장비 평균 출력은 145W 밖에 안되고 몇주 뒤에 250W가 나오지만 어느쪽도 상용화와는 거리가 있습니다.

올해 말 300W 장비가 나와야 비로소 사정이 좀 나아질겁니다. 또한 EUV 재료의 문제도 있습니다. 현재 자외선의 투과율은 83퍼센트 밖에 안되고 내년이 되어야

90퍼센트를 넘기게 됩니다.

(IP보기클릭)116.39.***.***

즉.... TSMC의 로드맵을 볼때 7나노 대비 5나노 공정은 희망적이지 못하고 다크실리콘 문제로 고성능 쪽은 엉망일 가능성이 아주 높다 라는 이야기가 많습니다. 역시나 미세공정은 어렵나봅니다

(IP보기클릭)116.39.***.***

(IP보기클릭)58.143.***.***

옛날처럼 공정 오른다고 성능이 막 오르지도 않는데 비해 난이도는 높은거 같아요. | 18.05.10 18:34 | | |

(IP보기클릭)116.39.***.***

게다가 공정개발 비용이 상승해서 칩 단가도 이전만큼 싸지지도 않죠.... | 18.05.10 18:46 | | |

(IP보기클릭)121.169.***.***

뭐 예전에 하는 말로는 12나노였나 7나노 부터는 미친듯이 어려워지고 5나노였던가 그 이하는 규소로는 못하고 다른 재료 찾아야 한다고 그러니... | 18.05.10 18:56 | | |

(IP보기클릭)222.118.***.***

이미 5나노 수준은 보통 원자 두께 20개 정도라.. 일반적인 반도체론 양자터널이 심해서 더 줄이긴 힘든데 다른 재료를 서서 양자터널을 더 최소화하고 그래핀처럼 단분자 두께를 실현해도 별 차이 안나겠죠.. 빨리 그래핀을 상용화 해야하는데 양산은 2014년 되었다는것 같은데 소식이 없으니 | 18.05.10 19:32 | | |

(IP보기클릭)54.95.***.***

EUV 양산 지연이 주 원인인데 다른 기업은 뭐 사정이 낫나요? 이미 무어의 법칙 사수하기도 쉽지 않은 상황입니다 | 18.05.11 00:32 | | |

(IP보기클릭)211.36.***.***

(IP보기클릭)103.5.***.***

(IP보기클릭)1.222.***.***

(IP보기클릭)175.223.***.***

(IP보기클릭)210.100.***.***