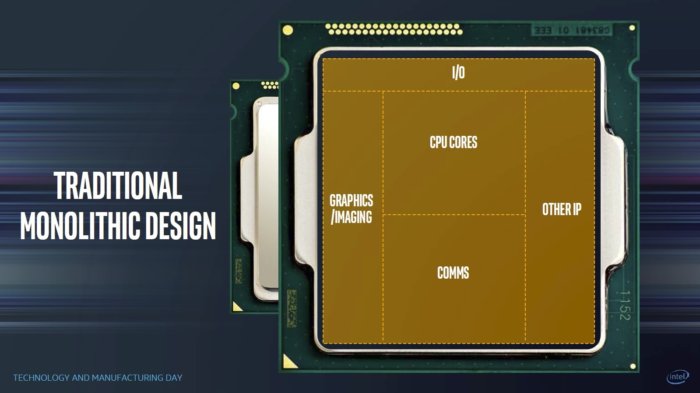

기존의 반도체들은 모두 같은 공정기술을 이용해서 패키징되어 왔습니다. 하지만 이런 방식은

특정부분에서 기술적인 문제가 발생을 할 경우에는 문제가 해결될때까지 기다려야만 하는 문제점을 가지고 있습니다.

이게 기존의 반도체의 패키징 방식입니다. 전부 같은 공정으로 만들어진 부품(?)을 하나로 패키징해서 만들어집니다.

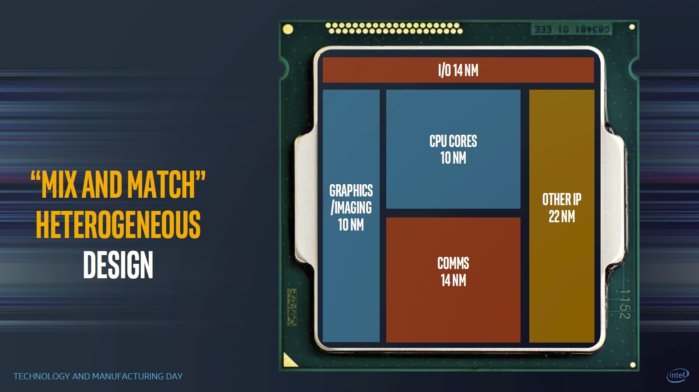

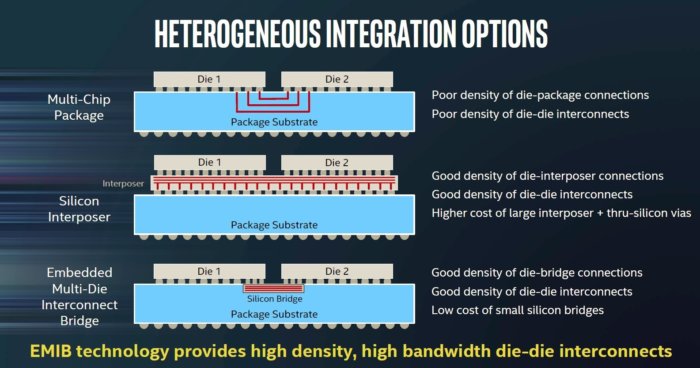

이게 인텔이 도입할 EMIB라는 방식입니다. Embedded Multi-die Interconnect Bridge의 약자입니다.

이 기술을 도입하는 제품은 서로 다른 공정으로 만들어진 반도체들을 하나의 다이에 패키징 하여 사용할 수 있도록 만들 수가 있습니다.

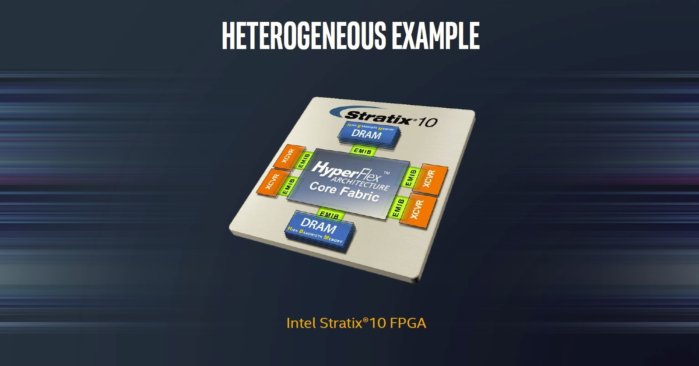

그리고 이 기술을 이용하면 HBM 같은 메모리도 쉽게 한 다이에 패키징을 할수도 있다고 합니다.

이미 이 기술을 적용한 제품은 이미 나와있는데 인텔이 인수한 알텔라의 Stratix 10 FPGA 칩입니다.

X86제품군에는 언제 적용을 할지는 아직 발표는 없습니다.

이 기술이 보급되면 대역폭으로 고생하는 APU나 위에 예를 든 부분적인 문제로 같은 공정으로 제품을 만들기 어려운때에

큰 힘을 발휘 할듯 보입니다.

(IP보기클릭)110.70.***.***

나도 암빠지만 이건 커버 못치겠다

(IP보기클릭)116.39.***.***

이게 잘못된 기술도 아닌데 왜 그래야하는지요. 그리고 이런 기술은 TSMC도 삼성도 연구 중입니다. 밑에 적은대로 기존 방식보다 더 저렴하게 HBM같은 메모리도 패키징이 가능하거든요. 그리고 앞으로의 반도체들은 더 많은 제품들과도 연결되어야 합니다. 이런 기술은 필수요소죠.

(IP보기클릭)116.39.***.***

그 보다는 이전공정의 반도체를 적용해도 충분한걸 활용해서 수율해결및 원가 절감을 한다는거죠.

(IP보기클릭)116.38.***.***

To 아마노 : 아.. 제 말은.. "기술"을 말하는게 아니라;; 가격입니다... 나오고 또 당분간은 가격이 올라가는걸 생각했습니다~

(IP보기클릭)116.39.***.***

그리고 HBM같은 대역폭이 넓은 메모리를 저렴하고 간단하게 패키징 할 수 있데 함으로써 단가에도 큰 공헌을 할 수 있는 기술입니다.

(IP보기클릭)110.70.***.***

(IP보기클릭)183.105.***.***

그래픽작업에 라데온 | 17.03.29 19:58 | | |

(IP보기클릭)1.227.***.***

(IP보기클릭)59.17.***.***

인텔이 나쁜 마음먹고 그런다면 가능할지도 모르겠네요. | 17.03.29 19:18 | | |

(IP보기클릭)116.39.***.***

그 보다는 이전공정의 반도체를 적용해도 충분한걸 활용해서 수율해결및 원가 절감을 한다는거죠. | 17.03.29 19:18 | | |

(IP보기클릭)1.227.***.***

요즘 인텔 하는 꼬라지보면 99%아닌가요 ㅋㅋ | 17.03.29 19:18 | | |

(IP보기클릭)1.227.***.***

하위 셀러론같은거엔 hd4400같은 하스웰시절 내장그래픽박고그럴수도잇겟군요 | 17.03.29 19:29 | | |

(IP보기클릭)116.39.***.***

그리고 HBM같은 대역폭이 넓은 메모리를 저렴하고 간단하게 패키징 할 수 있데 함으로써 단가에도 큰 공헌을 할 수 있는 기술입니다. | 17.03.29 19:32 | | |

(IP보기클릭)211.216.***.***

인텔이 예전부터 말한 진정한 SoC하려면 꼭 필요한 기술입니다. 다른공정은 위 말한거 처럼 파운더리 공정도 가능하지만, 가장 중요한 d램과 낸드와 같은 제작 방식이 다른 칩까지도 on-die 비슷한 성능으로 저렴하게 집적가능하다는게(AMD 인터 커넥터보다는 못하고 MCP보다는 좋은 성능) 가장 중요한 포인트입니다. 그리고 전공정은 지금도 많이 이용되고 있는데(CPU만 한 4년 찍고 폐쇠하기엔 현실적으로 너무 돈 낭비 아닌가요? 그런 비용이 다 가격에 청구될텐데...), 보통 PCH와 컨트롤러 부분은 전공정으로 사용하고, 그래픽스도 솔직히 전공정으로 돌릴수 있지만, 원가상으로 전공정쓰는게 더 비용이 많이 드는데, 하위 모델에 넣을리가 만무하다 보네요.(PAO에서 O단계에서 전 라인업의 그래픽스를 전 공정으로 돌리면 돌렸지 하위용 상위용 해서 이원화 공정에 생산하는게 단일 공정에 비해 유지와 관리(계속 생산하려면 품질이나 수율등의 이유로 스태핑을 각 라인별로 계속 개발해야 합니다.) 비용도 추가로 들기 때문에 다이도 더커지고 비용도 더 드는데 굳이 나눌 확률은 극히 적다 봅니다.) | 17.03.30 01:43 | | |

(IP보기클릭)116.38.***.***

(IP보기클릭)116.39.***.***

이게 잘못된 기술도 아닌데 왜 그래야하는지요. 그리고 이런 기술은 TSMC도 삼성도 연구 중입니다. 밑에 적은대로 기존 방식보다 더 저렴하게 HBM같은 메모리도 패키징이 가능하거든요. 그리고 앞으로의 반도체들은 더 많은 제품들과도 연결되어야 합니다. 이런 기술은 필수요소죠. | 17.03.29 19:24 | | |

(IP보기클릭)116.38.***.***

天ノ川沙夜

To 아마노 : 아.. 제 말은.. "기술"을 말하는게 아니라;; 가격입니다... 나오고 또 당분간은 가격이 올라가는걸 생각했습니다~ | 17.03.29 19:26 | | |

(IP보기클릭)116.39.***.***

이 기술은 칩 가격에 경쟁력을 줄 기술입니다. 기존의 방식보다 저렴하고 쉽게 각 반도체들을 연결해주는 기술이거든요. | 17.03.29 19:33 | | |

(IP보기클릭)116.38.***.***

네~ 맞아요.. 처음 인텔이 이 기술로 CPU를 만든후.. 추후 AMD에서도 CPU를 내어서 이번 에 "라이전"효과처럼.. CPU가격에 거품을 빼고.. 좋은 전쟁 펼쳤스면 합니다~ | 17.03.29 19:40 | | |

(IP보기클릭)116.39.***.***

네 그게 모든 소비자가 득을 보는 길이죠. | 17.03.29 19:41 | | |

(IP보기클릭)58.143.***.***

필요한 부분에 필요한 기술이 들어가는거라 개발단가가 낮아질 수 있으니 나쁘지 않은 방향으로 봄. | 17.03.29 19:42 | | |

(IP보기클릭)116.38.***.***

맞는말입니다.. 그래서 AMD 분발하여서.. 이번에 CPU가격도 낮아지고~ 인텔만의 독주와 거품피해가 없었슴 하는것이죠~ 기대돼는 기술이죠! | 17.03.29 19:58 | | |

(IP보기클릭)116.38.***.***

초반엔 가격이 상당수 있을듯 해요.. 괴거 SSD 128GB가 초특급가격이였죠 (얼마더라;; 비샀던;;;) 허나.. 현재 3D NAND기술로써 가격은 더 낮아지고 성능은 좋아지고(TLC주제에 성능은 MLC급) 앞으로 더~ 좋아지긴 할듯 한데... 가격이..ㅠ_ㅠ | 17.03.29 20:00 | | |

(IP보기클릭)175.206.***.***

(IP보기클릭)121.181.***.***

(IP보기클릭)58.143.***.***

(IP보기클릭)110.70.***.***

(IP보기클릭)58.143.***.***

확실히 저렇게 가면 개발속도 빨라질거라고 봄. 근데 나쁜점은 수많은 중간업글과 리버전이 나올 수 있다는 거겠죠. ㅎㅎ | 17.03.29 19:47 | | |

(IP보기클릭)110.70.***.***

안해도 이미 중간 업글 끝없이 하는데료 뭘..... 그럴일은 없겠지만 저것으로 인해 제조상 단가가 떨어지면 가격이 떨어지...진않겠지만 오르진않겠죠 뭐 | 17.03.29 19:53 | | |

(IP보기클릭)182.211.***.***

조금 무식한 방법이긴 하지만 MCP(Multiple Chip Package)란 기술이 있습니다. 단지 MCP으로는 내부 Chip간 연결이나 데이터 전송에 한계가 있죠 | 17.03.29 20:08 | | |

(IP보기클릭)110.70.***.***

뭐 예전의 코어2쿼드나 옵테론 같은놈 말씀하시는거죠?? | 17.03.29 20:10 | | |

(IP보기클릭)182.211.***.***

https://www.google.co.kr/search?q=Multiple+Chip+Package&tbm=isch&imgil=Ov8335tvMRimVM%253A%253BW9PZEURj3ZYaNM%253Bhttp%25253A%25252F%25252Fwww.fudzilla.com%25252F26786-intel-migrates-to-desktop-multi-chip-module-mcm-with-14nm-broadwell&source=iu&pf=m&fir=Ov8335tvMRimVM%253A%252CW9PZEURj3ZYaNM%252C_&usg=__zxH05RQO0kVal1FGeSav4myBzGw%3D&biw=1010&bih=1051&ved=0ahUKEwiIiJ6myfvSAhUJrY8KHQ_3DX4QyjcISg&ei=bJXbWIiiIYnavgSP7rfwBw#imgrc=Ov8335tvMRimVM:&spf=192 요론 놈입니다. 칩 2개를 만들어서 패키징(보통 까만거) 속에 두개를 넣어버리는거죠 | 17.03.29 20:13 | | |

(IP보기클릭)110.70.***.***

아름다운 power가 보이는것 보니 대충 예상이 맞는거 같네요. 설명 감사합니다 | 17.03.29 20:18 | | |

(IP보기클릭)182.211.***.***

으음 코어2쿼드나 인텔의 일반적인 디지털 프로세서 칩은 다 싱글칩 인걸로 압니다. 저건 통신 아날로그 모듈이 디지털칩 노이즈에 취약해서 MCP를 한거고요... | 17.03.29 20:21 | | |

(IP보기클릭)182.211.***.***

아 저 사진은 CPU + GPU네요 샌디부터 하나로 합쳐졌고요 | 17.03.29 20:22 | | |

(IP보기클릭)110.70.***.***

코어2쿼드는 투다이라고 알고있는데 이럼에도 싱글 칩이라고 할수 있나요? | 17.03.29 20:23 | | |

(IP보기클릭)182.211.***.***

The single- and dual-core models are single-die, whereas the quad-core models comprise two dies, each containing two cores, packaged in a multi-chip module. 오호 코어2쿼드는 MCM 방식이었네요, 사실 이때는 크고 아름다운 디지털을 만들면 수율이 떨어져서 저렇게 한 거가 아닐까 생각합니다. 하지만 같은 디지털을 MCM으로 잇는건 별로 바람직한건 아니죠 ㅎ | 17.03.29 20:28 | | |

(IP보기클릭)211.216.***.***

칩이라는 용어가 다이 뿐만 아니라 패키지를 지칭하기도 해서 생기는 문제입니다. 원래는 보통 칩=다이로 보시는 분은 싱글 칩 마이크로 프로세서의 칩으로 (다이)을 지칭하는 용어로도 봅니다. MCP와 MCM의 MC가 멀티 칩의 준말인 이유구요(이것도 문제인게... IC의 범주내에서 싱글칩 마이크로프로세서는 싱글 다이라는 점이 아니라 단일 패키지로 프로세싱 가능해서 싱글칩인데.. 초기부터 마이크로프로세서는 싱글 다이로 이루어져서 싱글패키지=싱글다이로 보면서 이런 혼란이.....) 하지만, 칩은 IC를 가리키기 때문에, IC 내부는 단일 다이 외에도 각각 독립된 회로의 여러 다이을 와이어 본딩으로 된 한개 패키지를 싱글 IC=칩 가리키지도 해서 Soc나 HBM등이 POP와같은 적층형 제품에 싱글 칩이라고 하면 싱글 패키지를 말하는거라 생각하시면 되구요. 그래서 과거로 가면 팬티엄2,3(슬롯 제품군으로 팬3 카트마이까지 cpu+L2캐쉬) 팬티엄D, 코어2쿼드는(cpu+cpu) 클락데일(CPU GPU), 샌디이후 -U라인업 이하(CPU +PCH)와 eDRAM모델도 MCP인데 싱글칩이라고도 부르는 이유가 패키지로 지칭하기 때문입니다. | 17.03.30 02:27 | | |

(IP보기클릭)182.211.***.***

(IP보기클릭)110.70.***.***

루리웹-3599871068

나도 암빠지만 이건 커버 못치겠다 | 17.03.29 20:18 | | |

(IP보기클릭)121.190.***.***

AMD는 죽다 살아났는데 뭘 따라오고 자시고..; | 17.03.29 21:08 | | |

(IP보기클릭)124.199.***.***

AMD가 못따라옴 | 17.03.30 05:56 | | |

(IP보기클릭)14.45.***.***

(IP보기클릭)14.45.***.***

저 떔방을 X86에도 적용 한다면 캐논레이크는 14나노+10나노 반쪽짜리 가 되어 버린다는 것임. | 17.03.29 21:42 | | |

(IP보기클릭)112.168.***.***

굳이 공정으로 얻는 이득이 적은 곳까지 10나노여야할 필요가....? 인텔도 멍청한게 아니라면 공정상 이득 얻는부위 못얻는부위 잘 가려내서 할겁니다. | 17.03.30 00:25 | | |

(IP보기클릭)14.45.***.***

이미 자사에서 쓰지 않은 오래된 떡밥을 다시 꺼낸 것 부터 생각 해야 할점 이겠져. 기술적 한계. | 17.03.30 00:52 | | |

(IP보기클릭)112.168.***.***

오래된 떡밥을 꺼낼떈 크게 두가지죠 당시엔 그걸 실현할 기술적 경제적 이유가 없었거나 아니면 기술적 한계거나 근데 아무리 상황을 봐도 전자 개념이지 후자개념은 아니라고 보여지는데 말이죠. 위에 그림만봐도 직접적인 미세공정에 효과를 받는 GPU와 CPU쪽은 10나노 인것만 봐도 말이죠. 가장 어려운부분을 10나노로 처리한다는데 이경우 경제적관점인 영향이 크지 기술적 영향은 적다고 보입니다. | 17.03.30 01:13 | | |